# R1EX24002ASASOI R1EX24002ATASOI

Two-wire serial interface 2k EEPROM (256-word x 8-bit) R10DS0221EJ0200 Rev.2.00 Nov 07, 2013

### Description

R1EX24xxx series are two-wire serial interface EEPROM (Electrically Erasable and Programmable ROM). They realize high speed, low power consumption and a high level of reliability by employing advanced MONOS memory technology and CMOS process and low voltage circuitry technology. They also have a 16-byte page programming function to make their write operation faster.

### Features

- Single supply: 1.8 V to 5.5 V

- Two-wire serial interface (I<sup>2</sup>C serial bus)

- Clock frequency: 400 kHz

- Power dissipation:

- Standby: 2.0 µA (max)

- Active (Read): 1.0 mA (max)

- Active (Write): 2.5 mA (max)

- Automatic page write: 16-byte/page

- Write cycle time: 5 ms

- Endurance: 1,000k or more Cycles @25°C

- Data retention: 100 or more Years @25°C

- Small size packages: SOP-8pin, TSSOP-8pin

- Shipping tape and reel

- TSSOP 8-pin: 3,000 IC/reel

- Temperature range: -40 to +85°C

- Lead free products. (#U0, #S0)

- Halogen free products. (#U0)

### **Ordering Information**

|                        | Internal                | Package                                             |              | Shipping tape |

|------------------------|-------------------------|-----------------------------------------------------|--------------|---------------|

| Orderable Part Numbers | organization            |                                                     | Halogen free | and reel      |

| R1EX24002ASAS0I#U0     | 2k bit                  | 150 mil 8-pin plastic SOP<br>PRSP0008DF-B (FP-8DBV) | 0            | 2,500 IC/reel |

| R1EX24002ASAS0I#S0     | (256 × 8-bit)           | Lead free                                           | —            |               |

| R1EX24002ATAS0I#U0     | 2k bit<br>(256 × 8-bit) | 8-pin plastic TSSOP<br>PTSP0008JC-B (TTP-8DAV)      | 0            | 3,000 IC/reel |

| R1EX24002ATAS0I#S0     | (200 × 0-bit)           | Lead free                                           | _            |               |

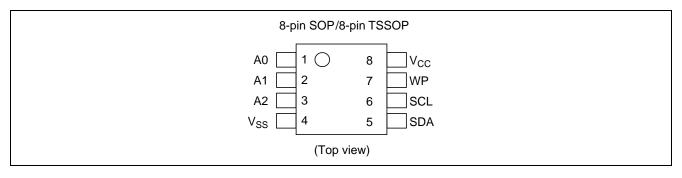

### **Pin Arrangement**

### **Pin Description**

| Pin name        | Function                 |

|-----------------|--------------------------|

| A0 to A2        | Device address           |

| SCL             | Serial clock input       |

| SDA             | Serial data input/output |

| WP              | Write protect            |

| V <sub>CC</sub> | Power supply             |

| V <sub>SS</sub> | Ground                   |

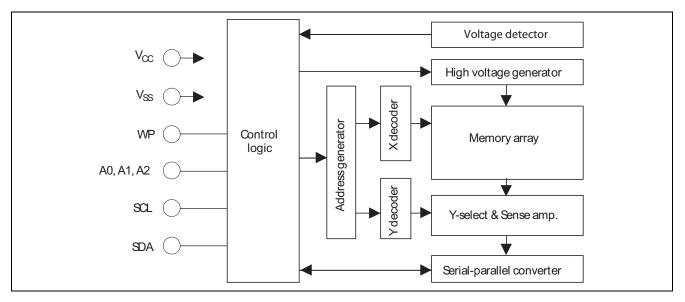

### **Block Diagram**

### **Absolute Maximum Ratings**

| Parameter                                  | Symbol          | Value                      | Unit |

|--------------------------------------------|-----------------|----------------------------|------|

| Supply voltage relative to V <sub>SS</sub> | V <sub>CC</sub> | –0.6 to +7.0               | V    |

| Input voltage relative to V <sub>SS</sub>  | Vin             | –0.5* <sup>2</sup> to +7.0 | V    |

| Operating temperature range* <sup>1</sup>  | Topr            | -40 to +85                 | °C   |

| Storage temperature range                  | Tstg            | –55 to +125                | °C   |

Notes: 1. Including electrical characteristics and data retention.

2. Vin (min): -3.0 V for pulse width  $\leq$  50 ns.

### **DC Operating Conditions**

| Parameter             | Symbol          | Min                | Тур | Max                   | Unit |

|-----------------------|-----------------|--------------------|-----|-----------------------|------|

| Supply voltage        | V <sub>CC</sub> | 1.8                | —   | 5.5                   | V    |

|                       | V <sub>SS</sub> | 0                  | 0   | 0                     | V    |

| Input high voltage    | V <sub>IH</sub> | $V_{CC} 	imes 0.7$ | —   | V <sub>CC</sub> + 0.5 | V    |

| Input low voltage     | VIL             | -0.3* <sup>1</sup> | —   | $V_{CC} \times 0.3$   | V    |

| Operating temperature | Topr            | -40                | _   | +85                   | °C   |

Note: 1.  $V_{IL}$  (min): -1.0 V for pulse width  $\leq$  50 ns.

### **DC Characteristics**

$(Ta = -40 \text{ to } +85^{\circ}\text{C}, V_{CC} = 1.8 \text{ V to } 5.5 \text{ V})$ **Test conditions** Parameter Symbol Min Max Unit Тур V<sub>CC</sub> = 5.5 V, Vin = 0 to 5.5 V Input leakage current  $I_{LI}$ 2.0 μΑ Output leakage current V<sub>CC</sub> = 5.5 V, Vout = 0 to 5.5 V  $I_{LO}$ \_\_\_\_ \_\_\_\_ 2.0 μΑ Standby V<sub>CC</sub> current 2.0  $V_{CC}$  = 5.5 V, Vin =  $V_{SS}$  or  $V_{CC}$ 1.0 μΑ I<sub>SB</sub> 0.5  $V_{CC}$  = 3.3 V, Vin =  $V_{SS}$  or  $V_{CC}$ , Ta=25°C μΑ Read V<sub>CC</sub> current 1.0  $V_{CC}$  = 5.5 V, Read at 400 kHz I<sub>CC1</sub> \_\_\_\_ \_\_\_\_ mΑ  $V_{CC}$  = 3.3 V, Read at 400 kHz, Ta= $25^{\circ}C$ 0.2 mΑ \_\_\_\_ Write V<sub>CC</sub> current I<sub>CC2</sub> \_\_\_\_ \_ 2.5 mΑ V<sub>CC</sub> = 5.5 V, Write at 400 kHz V<sub>CC</sub> = 3.3 V, Write at 400 kHz, Ta=25°C 1.0 mΑ Output low voltage  $V_{OL2}$ 0.4 V  $V_{CC}$  = 2.7 to 5.5 V,  $I_{OL}$  = 3.0 mA \_\_\_\_ \_\_\_\_ V  $V_{CC}$  = 1.8 to 2.7 V,  $I_{OL}$  = 1.5 mA V<sub>OL1</sub> \_\_\_\_ 0.2

### Capacitance

$(Ta = +25^{\circ}C, f = 1 \text{ MHz})$

| Parameter                             | Symbol                          | Min | Тур | Max | Unit | Test<br>conditions |

|---------------------------------------|---------------------------------|-----|-----|-----|------|--------------------|

| Input capacitance (A0 to A2, SCL, WP) | Cin* <sup>1</sup>               | _   |     | 6.0 | pF   | Vin = 0 V          |

| Output capacitance (SDA)              | C <sub>I/O</sub> * <sup>1</sup> | _   |     | 6.0 | pF   | Vout = 0 V         |

Note: 1. Not 100% tested.

### **Memory Cell Characteristics**

$(V_{CC} = 1.8 \text{ V to } 5.5 \text{ V})$

|                | <b>Ta=25</b> °C    | <b>Ta=85</b> °C | Notes |

|----------------|--------------------|-----------------|-------|

| Endurance      | 1,000k Cycles min. | 100k Cycles min | 1     |

| Data retention | 100 Years min.     | 10 Years min.   | 1     |

Note: 1. Not 100% tested.

### Data of shipped sample

All bits of EEPROM are logical "1" (FF Hex) at shipment.

### **AC Characteristics**

#### **Test Conditions**

• Input pules levels:

$-V_{IL} = 0.2 \times V_{CC}$

- V<sub>IH</sub> = 0.8 × V<sub>CC</sub>

- Input rise and fall time:  $\leq 20$  ns

- Input and output timing reference levels:  $0.5 \times V_{CC}$

- Output load: TTL Gate + 100 pF

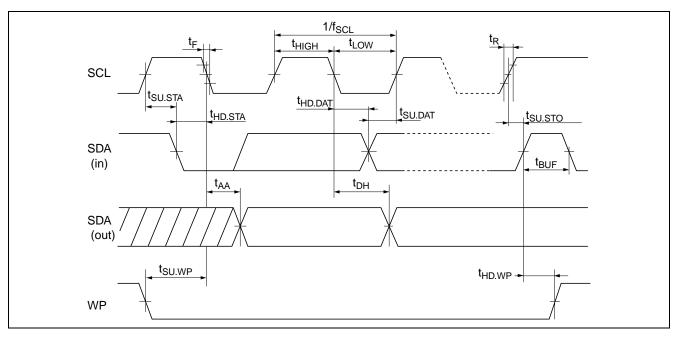

| Parameter                   | Symbol              | Min  | Тур | Max | Unit | Notes |

|-----------------------------|---------------------|------|-----|-----|------|-------|

| Clock frequency             | f <sub>SCL</sub>    |      |     | 400 | kHz  |       |

| Clock pulse width low       | t <sub>LOW</sub>    | 1200 |     |     | ns   |       |

| Clock pulse width high      | t <sub>ніGн</sub>   | 600  |     |     | ns   |       |

| Noise suppression time      | tı                  |      |     | 50  | ns   | 1     |

| Access time                 | t <sub>AA</sub>     | 100  | _   | 900 | ns   |       |

| Bus free time for next mode | t <sub>BUF</sub>    | 1200 | _   | _   | ns   |       |

| Start hold time             | t <sub>hd.sta</sub> | 600  |     |     | ns   |       |

| Start setup time            | t <sub>su.sta</sub> | 600  | _   | _   | ns   |       |

| Data in hold time           | t <sub>HD.DAT</sub> | 0    | _   | _   | ns   |       |

| Data in setup time          | t <sub>su.dat</sub> | 100  | _   | _   | ns   |       |

| Input rise time             | t <sub>R</sub>      | _    | _   | 300 | ns   | 1     |

| Input fall time             | t <sub>F</sub>      | _    | _   | 300 | ns   | 1     |

| Stop setup time             | t <sub>su.sto</sub> | 600  | _   | _   | ns   |       |

| Data out hold time          | t <sub>DH</sub>     | 50   | _   | _   | ns   |       |

| Write protect hold time     | t <sub>HD.WP</sub>  | 1200 | _   | _   | ns   |       |

| Write protect setup time    | t <sub>SU.WP</sub>  | 0    | _   | _   | ns   |       |

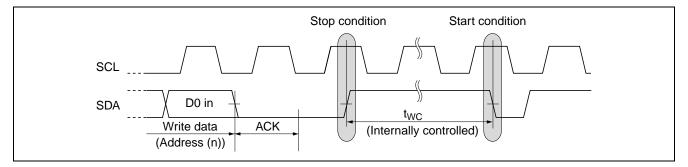

| Write cycle time            | twc                 |      |     | 5   | ms   | 2     |

Notes: 1. Not 100% tested.

2.  $t_{WC}$  is the time from a stop condition to the end of internally controlled write cycle.

$(Ta = -40 \text{ to } +85^{\circ}C, V_{CC} = 1.8 \text{ to } 5.5 \text{ V})$

### Timing Waveforms

### **Bus Timing**

### Write Cycle Timing

### **Pin Function**

#### Serial Clock (SCL)

The SCL pin is used to control serial input/output data timing. The SCL input is used to positive edge clock data into EEPROM device and negative edge clock data out of each device. Maximum clock rate is 400 kHz.

#### Serial Input/Output Data (SDA)

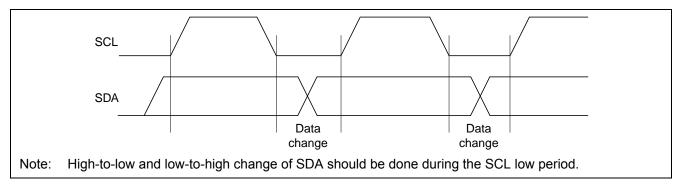

The SDA pin is bidirectional for serial data transfer. The SDA pin needs to be pulled up by resistor as that pin is opendrain driven structure. Use proper resistor value for your system by considering  $V_{OL}$ ,  $I_{OL}$  and the SDA pin capacitance. Except for a start condition and a stop condition which will be discussed later, the SDA transition needs to be completed during the SCL low period.

#### Data Validity (SDA data change timing waveform)

#### Device Address (A0, A1, A2)

Eight devices can be wired for one common data bus line as maximum. Device address pins are used to distinguish each device address pins should be connected to  $V_{CC}$  or  $V_{SS}$ . When device address code provided from SDA pin matches corresponding hard-wired device address pins A0 to A2, that one device can be activated. These pins are internally pulled-down to  $V_{SS}$ . The device reads these pins as Low if unconnected.

#### Pin Connections for A0 to A2

|             | Max connect | Pin connection                   |                                  |                                  |      |

|-------------|-------------|----------------------------------|----------------------------------|----------------------------------|------|

| Memory size | number      | A2                               | A1                               | A0                               | Note |

| 2k bit      | 8           | V <sub>CC</sub> /V <sub>SS</sub> | V <sub>CC</sub> /V <sub>SS</sub> | V <sub>CC</sub> /V <sub>SS</sub> |      |

Notes: 1. During floating, " $V_{CC}/V_{SS}$ " are fixed to  $V_{SS}$ , because these are internally pulled-down.

#### Write Protect (WP)

When the Write Protect pin (WP) is high, the write protection feature is enabled and operates as shown in the following table.

Also, acknowledgment "0" is outputted after inputting device address and memory address. After inputting write data, acknowledgment "1""(**NO ACK**) is outputted.

When the WP is low, write operation for all memory arrays are allowed. The read operation is always activated irrespective of the WP pin status.

The WP pin is internally pulled-down to V<sub>SS</sub>. Write operations for all memory array are allowed if unconnected.

#### Write Protect Area

|                 | Write protect area          |

|-----------------|-----------------------------|

| WP pin status   | 2k bit                      |

| V <sub>IH</sub> | Full (2k bit)               |

| VIL             | Normal read/write operation |

### **Functional Description**

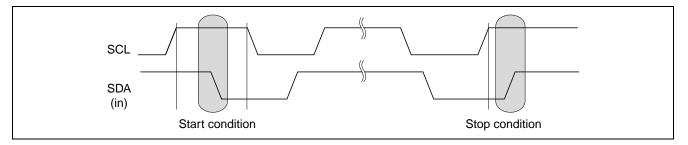

#### **Start Condition**

A high-to-low transition of the SDA with the SCL high is needed in order to start read, write operation (See start condition and stop condition).

#### **Stop Condition**

A low-to-high transition of the SDA with the SCL high is a stop condition. The stand-by operation starts after a read sequence by a stop condition. In the case of write operation, a stop condition terminates the write data inputs and place the device in a internally-timed write cycle to the memories. After the internally-timed write cycle which is specified as  $t_{WC}$ , the device enters a standby mode (See write cycle timing).

#### **Start Condition and Stop Condition**

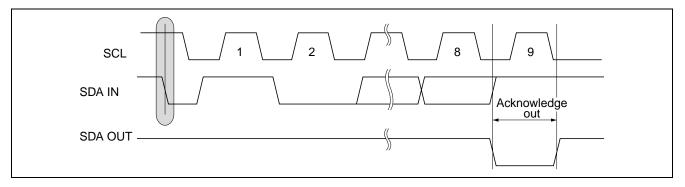

#### Acknowledge

All addresses and data words are serially transmitted to and from in 8-bit words. The receiver sends a zero to acknowledge that it has received each word. This happens during ninth clock cycle. The transmitter keeps bus open to receive acknowledgment from the receiver at the ninth clock. In the write operation, EEPROM sends a zero to acknowledge after receiving every 8-bit words. In the read operation, EEPROM sends a zero to acknowledge after receiving the device address word. After sending read data, the EEPROM waits acknowledgment by keeping bus open. If the EEPROM receives zero as an acknowledge, it sends read data of next address. If the EEPROM receives acknowledgment "1" (no acknowledgment) and a following stop condition, it stops the read operation and enters a stand-by mode. If the EEPROM receives neither acknowledgment "0" nor a stop condition, the EEPROM keeps bus open without sending read data.

#### Acknowledge Timing Waveform

#### **Device Addressing**

The EEPROM device requires an 8-bit device address word following a start condition to enable the chip for a read or a write operation. The device address word consists of 4-bit device code, 3-bit device address code and 1-bit read/write(R/W) code. The most significant 4-bit of the device address word are used to distinguish device type and this EEPROM uses "1010" fixed code. The device address word is followed by the 3-bit device address code A2, A1, A0. The device address code selects one device out of eight devices which are connected to the bus. This means that the device is selected if the inputted 3-bit device address code is equal to the corresponding hard-wired A2 to A0 pins status. The eighth bit of the device address word is the read/write(R/W) bit. A write operation is initiated if this bit is "0" and a read operation is initiated if this bit is "1". The EEPROM turns to a stand-by state if the device code is not "1010" or device address code doesn't coincide with status of the correspond hard-wired device address pins.

#### **Device Address Word**

|    |                     | Device address word (8-bit) |             |                     |    |    |                        |     |

|----|---------------------|-----------------------------|-------------|---------------------|----|----|------------------------|-----|

|    | Device code (fixed) |                             |             | Device address code |    |    | R/W code* <sup>1</sup> |     |

| 2k | 1                   | 0                           | 1           | 0                   | A2 | A1 | A0                     | R/W |

|    |                     |                             | <b>"0</b> " |                     |    |    |                        |     |

Note: 1. R/W="1" is read and R/W = "0" is write.

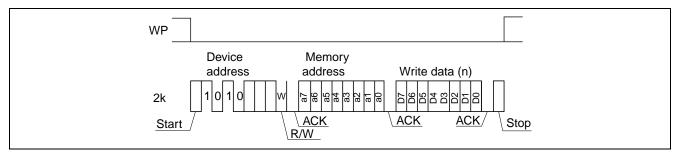

#### Write Operations (WP=Low)

#### Byte Write: (Write operation during WP=Low status)

A write operation requires an 8-bit device address word with R/W = "0". Then the EEPROM sends acknowledgment "0" at the ninth clock cycle. After these, the 2k bit EEPROM receives 8-bit memory address words. Upon receipt of this memory address, the EEPROM outputs acknowledgment "0" and receives a following 8-bit write data. After receipt of write data, the EEPROM outputs acknowledgment "0". If the EEPROM receives a stop condition, the EEPROM enters an internally-timed write cycle and terminates receipt of SCL, SDA inputs until completion of the write cycle. The EEPROM returns to a standby mode after completion of the write cycle.

#### **Byte Write Operation**

#### Page Write:

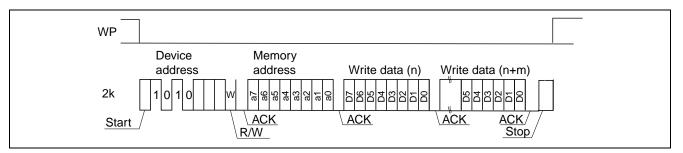

The EEPROM is capable of the page write operation which allows any number of bytes up to 16 bytes to be written in a single write cycle. The page write is the same sequence as the byte write except for inputting the more write data. The page write is initiated by a start condition, device address word, memory address(n) and write data (Dn) with every ninth bit acknowledgment. The EEPROM enters the page write operation if the EEPROM receives more write data (Dn+1) instead of receiving a stop condition. The a0 to a3 address bits are automatically incremented upon receiving write data (Dn+1). The EEPROM can continue to receive write data up to 16 bytes. If the a0 to a3 address bits reaches the last address of the page, the a0 to a3 address bits will roll over to the first address of the same page and previous write data will be overwritten. Upon receiving a stop condition, the EEPROM stops receiving write data and enters internally-timed write cycle.

#### **Page Write Operation**

#### Write Operations (WP=High)

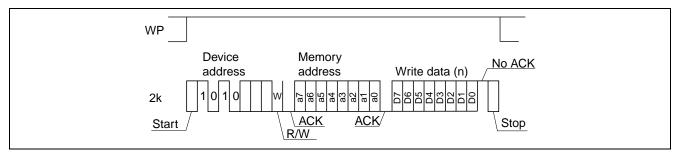

#### Byte Write: (Write operation during WP=High status)

A write operation requires an 8-bit device address word with R/W = "0". Then the EEPROM sends acknowledgment "0" at the ninth clock cycle. After these, the 2k bit EEPROM receives 8-bit memory address. Upon receipt of this memory address, the EEPROM outputs acknowledgment "0". After receipt of 8-bit write data, the EEPROM outputs acknowledgment "1"(**NO ACK**). Then the EEPROM write operations are not allowed.

#### **Byte Write Operation**

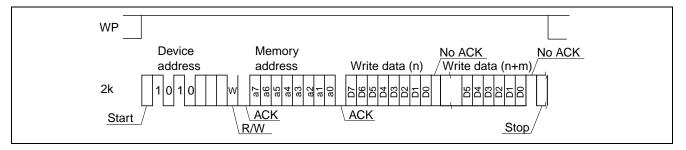

#### Page Write:

The page write is the same sequence as the byte write. The page write is initiated by a start condition, device address word and memory address(n) with every ninth bit acknowledgment"0". But after inputting write data(Dn), the EEPROM outputs acknowledgment "1"(**NO ACK**). Then the EEPROM write operations are not allowed.

#### **Page Write Operation**

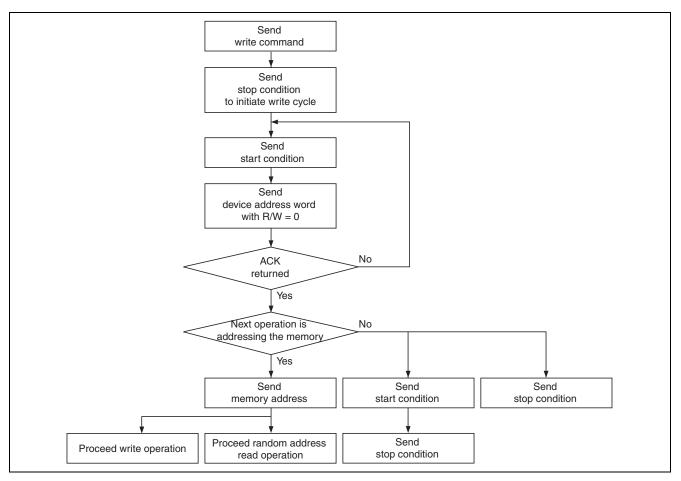

#### **Acknowledge Polling:**

Acknowledge polling feature is used to show if the EEPROM is in a internally-timed write cycle or not. This feature is initiated by the stop condition after inputting write data. This requires the 8-bit device address word following the start condition during a internally-timed write cycle. Acknowledge polling will operate when the R/W code = "0". Acknowledgment "1" (no acknowledgment) shows the EEPROM is in a internally-timed write cycle and acknowledgment "0" shows that the internally-timed write cycle has completed. See Write Cycle Polling using ACK.

#### Write Cycle Polling Using ACK

#### **Read Operation**

There are three read operations: current address read, random read, and sequential read. Read operations are initiated the same way as write operations with the exception of R/W = "1".

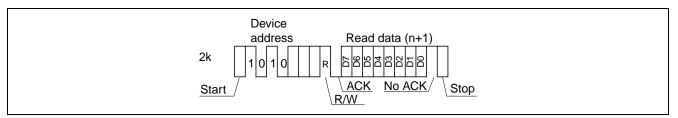

#### **Current Address Read:**

The internal address counter maintains the last address accessed during the last read or write operation, with incremented by one. Current address read accesses the address kept by the internal address counter. After receiving a start condition and the device address word (R/W is "1"), the EEPROM outputs the 8-bit current address data from the most significant bit following acknowledgment "0". If the EEPROM receives acknowledgment "1" (no acknowledgment) and a following stop condition, the EEPROM stops the read operation and is turned to a standby state. In case the EEPROM has accessed the last address of the last page at previous read operation, the current address will roll over and returns to zero address. In case the EEPROM has accessed the last address of the page at previous write operation, the current address will roll over within page addressing and returns to the first address in the same page. The current address is valid while power is on. The current address after power on will be indefinite. The random read operation described below is necessary to define the memory address.

#### **Current Address Read Operation**

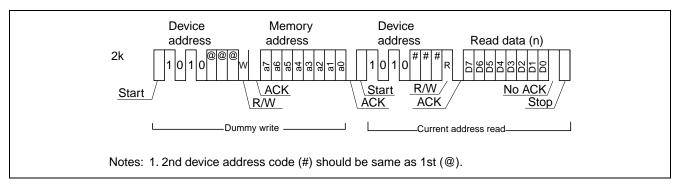

#### **Random Read:**

This is a read operation with defined read address. A random read requires a dummy write to set read address. The EEPROM receives a start condition, device address word (R/W=0) and memory address 8-bit sequentially. The EEPROM outputs acknowledgment "0" after receiving memory address then enters a current address read with receiving a start condition. The EEPROM outputs the read data of the address which was defined in the dummy write operation. After receiving acknowledgment "1"(no acknowledgment) and a following stop condition, the EEPROM stops the random read operation and returns to a standby state.

#### **Random Read Operation**

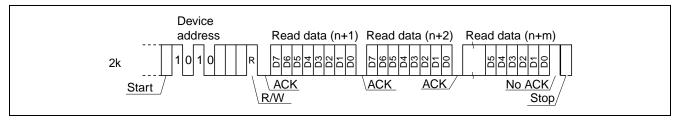

#### **Sequential Read:**

Sequential reads are initiated by either a current address read or a random read. If the EEPROM receives acknowledgment "0" after 8-bit read data, the read address is incremented and the next 8-bit read data are coming out. This operation can be continued as long as the EEPROM receives acknowledgment "0". The address will roll over and returns address zero if it reaches the last address of the last page. The sequential read can be continued after roll over. The sequential read is terminated if the EEPROM receives acknowledgment "1" (no acknowledgment) and a following stop condition.

#### **Sequential Read Operation**

### Notes

#### Data Protection at V<sub>cc</sub> On/Off

When  $V_{CC}$  is turned on or off, noise on the SCL and SDA inputs generated by external circuits (CPU, etc) may act as a trigger and turn the EEPROM to unintentional program mode. To prevent this unintentional programming, this EEPROM has a power on reset function. Be careful of the notices described below in order for the power on reset function to operate correctly.

- SCL and SDA should be fixed to  $V_{CC}$  or  $V_{SS}$  during  $V_{CC}$  on/off. Low to high or high to low transition during  $V_{CC}$  on/off may cause the trigger for the unintentional programming.

- V<sub>CC</sub> should be turned off after the EEPROM is placed in a standby state.

- V<sub>CC</sub> should be turned on from the ground level(V<sub>SS</sub>) in order for the EEPROM not to enter the unintentional programming mode.

- $V_{CC}$  turn on rate should be slower than 2  $\mu$ s/V.

### **Noise Suppression Time**

This EEPROM have a noise suppression function at SCL and SDA inputs, that cut noise of width less than 50 ns. Be careful not to allow noise of width more than 50 ns.

#### Power Source Noise Countermeasures

In order to suppress power-source-noise which causes malfunction of the device, it is recommended to put 0.1 $\mu$ F bypass-capacitor (such as a monolithic ceramic capacitor which has good high-frequency characteristics) between V<sub>CC</sub> and V<sub>SS</sub>, and shorten the wiring length between the capacitor and V<sub>CC</sub>/V<sub>SS</sub> terminals as much as possible.

#### **Device Address Input, Write Protect input**

You can use this device with device-address and write-protect pins open state, because these pins are pulled down inside of the device. However, we recommend you connect these pins to  $V_{CC}$  or  $V_{SS}$  to avoid malfunction due to noise.

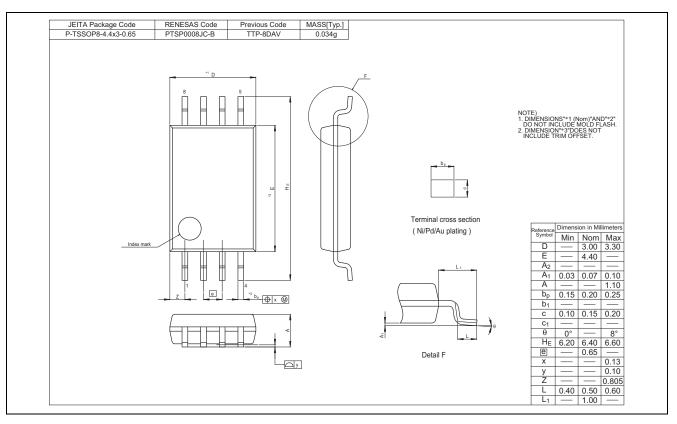

### **Package Dimensions**

#### RENESAS Code PRSP0008DF-B MASS[Typ.] 0.08g JEITA Package Code P-SOP8-3.9x4.89-1.27 Previous Code FP-8DBV NOTE) 1. DIMENSIONS"\*1 (Nom)"AND"\*2" DO NOT INCLUDE MOLD FLASH. 2. DIMENSION"\*3"DOES NOT INCLUDE TRIM OFFSET. f Index mark Terminal cross section (Ni/Pd/Au plating) Ħ Ħ Reference Dimension in Millimeters Min Nom Max — 4.89 5.15 — 3.90 e <sup>b</sup>₽ ⊕ × M D E A<sub>2</sub> A1 0.102 0.14 0.254 A — — 1.73 bp 0.35 0.40 0.45 - Ду Detail F 0.25 0.10 0.69 y Z L 0.406 0.60 0.889 L1 --- 1.06 ---

### R1EX24002ASAS0I (PRSP0008DF-B / Previous Code: FP-8DBV)

#### R1EX24002ATASOI (PTSP0008JC-B / Previous Code: TTP-8DAV)

**Revision History**

### R1EX24002ASAS0I/R1EX24002ATAS0I Data Sheet

|      |              | Description |                                                                                                          |  |  |

|------|--------------|-------------|----------------------------------------------------------------------------------------------------------|--|--|

| Rev. | Date         | Page        | Summary                                                                                                  |  |  |

| 1.00 | Oct 26, 2009 | _           | Initial issue                                                                                            |  |  |

| 2.00 | Nov 07, 2013 | 1           | Features                                                                                                 |  |  |

|      |              |             | Addition Halogen free                                                                                    |  |  |

|      |              | 2           | Ordering information: Change to orderable part number(#U0,#S0)                                           |  |  |

|      |              |             | Pin Arrangement: Change index position                                                                   |  |  |

|      |              |             | Addition Voltage detector in Block Diagram.                                                              |  |  |

|      |              | 3           | Addition DC characteristics                                                                              |  |  |

|      |              |             | I <sub>SB</sub> =0.5μA(Typ)@3.3V, I <sub>CC1</sub> =0.2mA(Typ)@3.3V, , I <sub>CC2</sub> =1.0mA(Typ)@3.3V |  |  |

|      |              |             | Addition Data shipment                                                                                   |  |  |

|      |              | 14          | Addition these items for Notes                                                                           |  |  |

|      |              |             | (Power Source Noise Countermeasures),                                                                    |  |  |

|      |              |             | (Device Address Input, Write Protect input)                                                              |  |  |

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or

- technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious properly damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics and amages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

#### SALES OFFICES

Refer to "http://www.renesas.com/" for the latest and detailed information

#### **Renesas Electronics Corporation**

http://www.renesas.com

Renesas Electronics America Inc. 2880 Scott Boulders: 1+408-588-6130 Renesas Electronics Canada Limited 1101 Nicholson Road, Newmarket, Ontario L3Y 9C3, Canada Tel: +1-905-898-5441, Fax: +1-905-898-3220 Renesas Electronics Compe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-651-700, Fax: +44-1628-651-804 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Disseldorf, Germany Tel: +49-211-65030, Fax: +44-1628-651-804 Renesas Electronics (Shanghai) Co., Ltd. 7th Floor, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100083, P.R.China Tel: +86-10-8235-1155, Fax: +86-10-823-7679 Renesas Electronics (Shanghai) Co., Ltd. 7th Floor, Quantum Tower, Sc55 LanGao Rd., Putuo District, Shanghai, China Tel: +86-10-8235-1155, Fax: +86-21-2226-0989 Renesas Electronics Hong Kong Limited Unit 1801-1613, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +88-10-824-1828-185, Fax: +86-28-12226-0999 Renesas Electronics Hong Kong Limited Unit 1801-1613, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +88-0-804-200, Fax: +86-24-27226-0999 Renesas Electronics Hong Kong Limited Unit 1801-1613, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +88-2886-9318, Fax: +86-28175-9670 Renesas Electronics Mang Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei, Taiwan Tel: +86-28-175-9600, Fax: +86-621-30300 Renesas Electronics Malaysia Sdn.Bhd 011 906, Block B, Menara Amoorp, Amoorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics Kona Co., Ltd. 2F., 234 Teheran-ro, Gangam-Gu, Seoul, 135-080, Korea Tel: +60-3-7955-9390, Fax: +60-3-7955-9510

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Renesas Electronics: <u>R1EX24002ATAS0I#S0</u> R1EX24002ASAS0I#S0