# SPC56EL70L3, SPC56EL70L5, SPC564L70L3, SPC564L70L5

## 32-bit Power Architecture<sup>®</sup>microcontroller for automotive SIL3/ASILD chassis and safety applications

Datasheet - production data

#### **Features**

- High-performance e200z4d dual core

- 32-bit Power Architecture<sup>®</sup> technology

CPU

- Core frequency as high as 120 MHz

- Dual issue five-stage pipeline core

- Variable Length Encoding (VLE)

- Memory Management Unit (MMU)

- 4 KB instruction cache with error detection code

- Signal Processing Engine (SPE)

- Memory available

- 2 MB flash memory with ECC

- 192 KB on-chip SRAM with ECC

- Built-in RWW capabilities for EEPROM emulation

- SIL3/ASILD innovative safety concept: Lock step mode and Fail-safe protection

- Sphere of Replication (SoR) for key components (such as CPU core, eDMA, crossbar switch)

- Fault Collection and Control Unit (FCCU)

- Redundancy Control and Checker Unit (RCCU) on outputs of the SoR connected to FCCU

- Boot-time Built-In Self-Test for Memory (MBIST) and Logic (LBIST) triggered by hardware

- Boot-time Built-In Self-Test for ADC and flash memory triggered by software

- Replicated safety enhanced watchdog

- Replicated junction temperature sensor

- Non Maskable Interrupt (NMI)

- 16-region Memory Protection Unit (MPU)

- Clock Monitoring Units (CMU)

- Power Management Unit (PMU)

- Cyclic Redundancy Check (CRC) unit

- Decoupled Parallel mode for high performance use of replicated cores

- Nexus Class 3+ interface

- Interrupts

- Replicated 16-priority controller

- Replicated 16-channel eDMA controller

- GPIOs individually programmable as input, output or special function

- Three 6-channel general-purpose eTimer units

- 2 FlexPWM units: Four 16-bit channels per module

- Communications interfaces

- 2 LINFlexD channels

- 3 DSPI channels with automatic chip select generation

- 3 FlexCAN interfaces (2.0B Active) with 32 message objects

- FlexRay module (V2.1 Rev. A) with 2 channels, 64 message buffers and data rates up to 10 Mbit/s

- Two 12-bit Analog-to-digital Converters (ADC)

- 16 input channels

- Programmable Cross Triggering Unit (CTU) to synchronize ADCs conversion with timer and PWM

- Sine wave generator (D/A with low pass filter)

- On-chip CAN/UART/FlexRay Bootstrap loader

- Single 3.0 V to 3.6 V voltage supply

- Ambient temperature range –40 °C to 125 °C

- Junction temperature range -40 °C to 150 °C

July 2015 DocID023953 Rev 5 1/128

### **Contents**

| 1 | Intro | duction |                                                                                        | 7  |

|---|-------|---------|----------------------------------------------------------------------------------------|----|

|   | 1.1   | Docum   | ent overview                                                                           | 7  |

|   | 1.2   | Descrip | otion                                                                                  | 7  |

|   | 1.3   | Device  | comparison                                                                             | 8  |

|   | 1.4   | Block o | liagram                                                                                | 11 |

|   | 1.5   | Feature | e details                                                                              | 12 |

|   | _     | 1.5.1   | High-performance e200z4d core                                                          |    |

|   |       | 1.5.2   | Crossbar switch (XBAR)                                                                 |    |

|   |       | 1.5.3   | Memory protection unit (MPU)                                                           |    |

|   |       | 1.5.4   | Enhanced direct memory access (eDMA)                                                   |    |

|   |       | 1.5.5   | On-chip flash memory with ECC                                                          |    |

|   |       | 1.5.6   | On-chip SRAM with ECC                                                                  |    |

|   |       | 1.5.7   | Platform flash memory controller                                                       | 15 |

|   |       | 1.5.8   | Platform static RAM controller (SRAMC)                                                 | 15 |

|   |       | 1.5.9   | Memory subsystem access time                                                           |    |

|   |       | 1.5.10  | Error correction status module (ECSM)                                                  | 16 |

|   |       | 1.5.11  | Peripheral bridge (PBRIDGE)                                                            | 17 |

|   |       | 1.5.12  | Interrupt controller (INTC)                                                            | 17 |

|   |       | 1.5.13  | System clocks and clock generation                                                     | 18 |

|   |       | 1.5.14  | Frequency-Modulated Phase-Locked Loop (FMPLL)                                          | 18 |

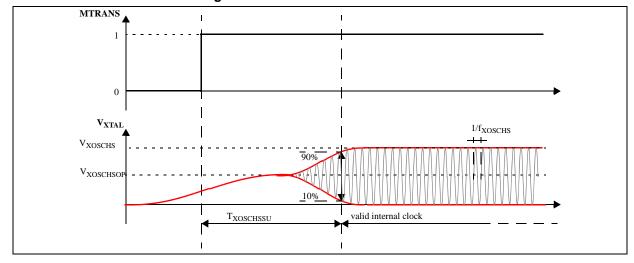

|   |       | 1.5.15  | Main oscillator                                                                        | 19 |

|   |       | 1.5.16  | Internal reference clock (RC) oscillator                                               | 19 |

|   |       | 1.5.17  | Clock, reset, power, mode and test control modules (MC_CGM, MC_RGM, MC_PCU, and MC_ME) | 19 |

|   |       | 1.5.18  | Periodic interrupt timer module (PIT)                                                  | 19 |

|   |       | 1.5.19  | System timer module (STM)                                                              | 20 |

|   |       | 1.5.20  | Software watchdog timer (SWT)                                                          | 20 |

|   |       | 1.5.21  | Fault collection and control unit (FCCU)                                               | 20 |

|   |       | 1.5.22  | System Integration Unit Lite (SIUL)                                                    | 20 |

|   |       | 1.5.23  | Non-maskable interrupt (NMI)                                                           | 21 |

|   |       | 1.5.24  | Boot assist module (BAM)                                                               | 21 |

|   |       | 1.5.25  | System status and configuration module (SSCM)                                          | 21 |

|   |       | 1.5.26  | FlexCAN                                                                                | 21 |

|   |       | 1.5.27  | FlexRay                                                                                | 23 |

|   |       |         |                                                                                        |    |

|   |       | 1.5.28    | Serial communication interface module (LINFlexD)                 | 24   |

|---|-------|-----------|------------------------------------------------------------------|------|

|   |       | 1.5.29    | Deserial serial peripheral interface (DSPI)                      | 25   |

|   |       | 1.5.30    | FlexPWM                                                          | 25   |

|   |       | 1.5.31    | eTimer module                                                    | 27   |

|   |       | 1.5.32    | Sine wave generator (SWG)                                        | 27   |

|   |       | 1.5.33    | Analog-to-Digital converter module (ADC)                         | 28   |

|   |       | 1.5.34    | Cross triggering unit (CTU)                                      | 28   |

|   |       | 1.5.35    | Cyclic redundancy checker (CRC) unit                             | 29   |

|   |       | 1.5.36    | Redundancy control and checker unit (RCCU)                       | 29   |

|   |       | 1.5.37    | Junction temperature sensor                                      |      |

|   |       | 1.5.38    | Nexus port controller (NPC)                                      |      |

|   |       | 1.5.39    | IEEE 1149.1 JTAG controller (JTAGC)                              |      |

|   |       | 1.5.40    | Voltage regulator / power management unit (PMU)                  |      |

|   |       | 1.5.41    | Built-In self-test (BIST) capability                             | 32   |

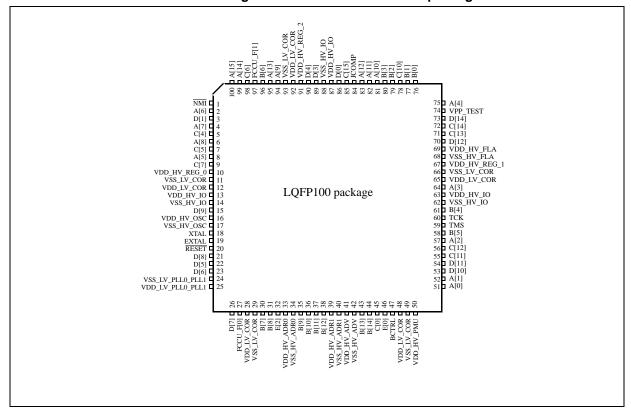

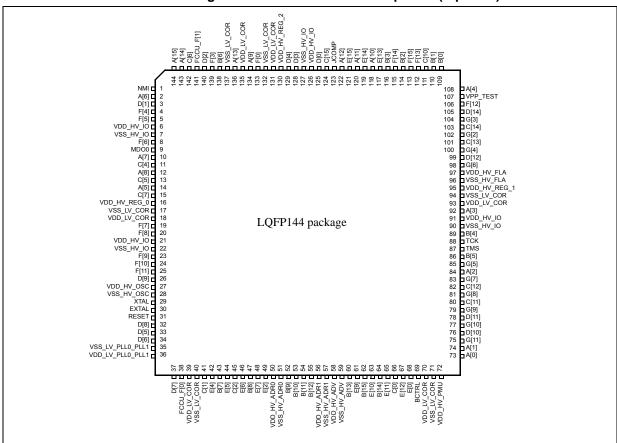

| 2 | Pack  | age pin   | outs and signal descriptions                                     | . 33 |

|   | 2.1   | Packag    | e pinouts                                                        | . 33 |

|   | 2.2   | Supply    | pins                                                             | . 54 |

|   | 2.3   | System    | pins                                                             | . 56 |

|   | 2.4   | Pin mux   | xing                                                             | . 57 |

| 3 | Elect | trical ch | aracteristics                                                    | . 74 |

|   | 3.1   | Introduc  | ction                                                            | . 74 |

|   | 3.2   | Absolut   | e maximum ratings                                                | . 74 |

|   | 3.3   |           | mended operating conditions                                      |      |

|   | 3.4   | Decoup    | oling capacitors                                                 | . 76 |

|   | 3.5   | Therma    | al characteristics                                               | . 79 |

|   |       | 3.5.1     | General notes for specifications at maximum junction temperature | 79   |

|   | 3.6   | Electron  | magnetic Interference (EMI) characteristics                      |      |

|   | 3.7   |           | static discharge (ESD) characteristics                           |      |

|   | 3.8   |           | atch-up (LU)                                                     |      |

|   | 3.9   |           | regulator electrical characteristics                             |      |

|   |       | •         | •                                                                |      |

|   | 3.10  |           | current characteristics                                          |      |

|   | 3.11  |           | rature sensor electrical characteristics                         |      |

|   | 3.12  | Main os   | scillator electrical characteristics                             | . 90 |

|   |       |           |                                                                  |      |

| 6 | Revi | sion his         | story                                      | 126 |

|---|------|------------------|--------------------------------------------|-----|

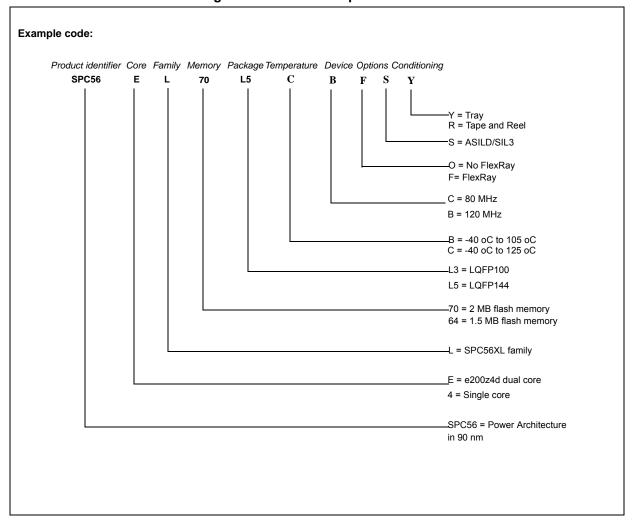

| 5 | Orde | ering inf        | formation                                  | 125 |

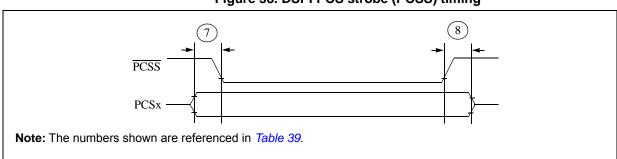

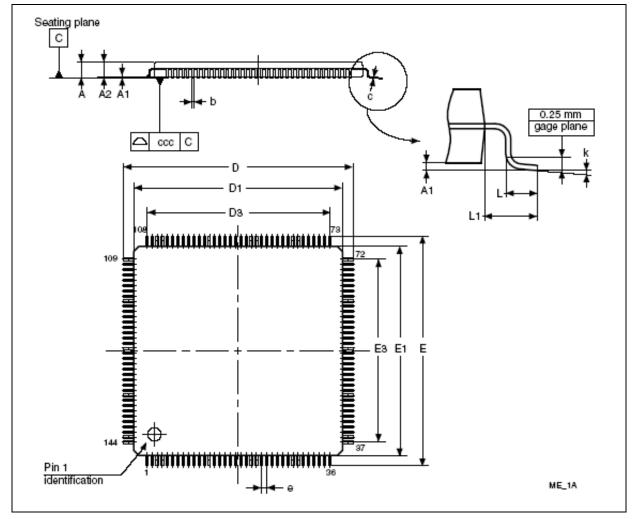

|   | 4.2  | Packag           | ge mechanical data                         | 121 |

|   | 4.1  |                  | ACK®                                       |     |

| 4 |      | •                | aracteristics                              |     |

|   |      | 0.20.0           | Doi running                                |     |

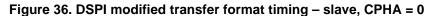

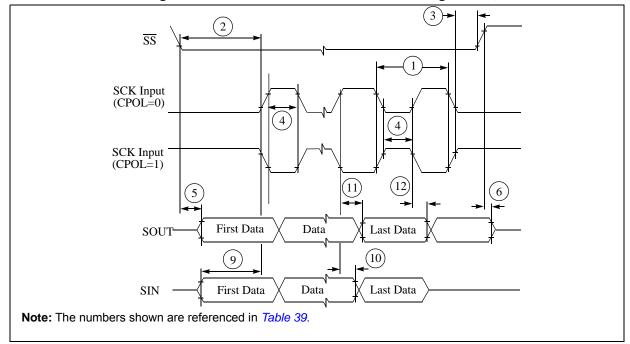

|   |      | 3.20.6           | DSPI timing                                |     |

|   |      | 3.20.4           | External interrupt timing (IRQ pin)        |     |

|   |      | 3.20.3           | IEEE 1149.1 JTAG interface timing          |     |

|   |      | 3.20.2<br>3.20.3 | WKUP/NMI timing                            |     |

|   |      | 3.20.1           | RESET pin characteristics                  |     |

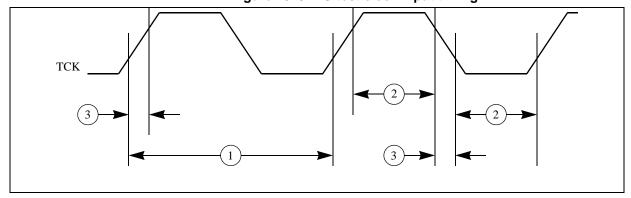

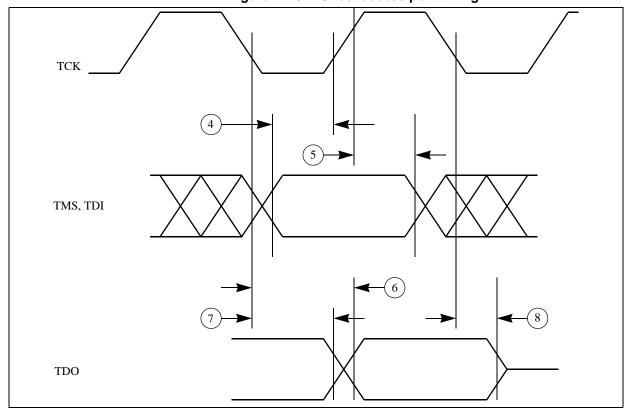

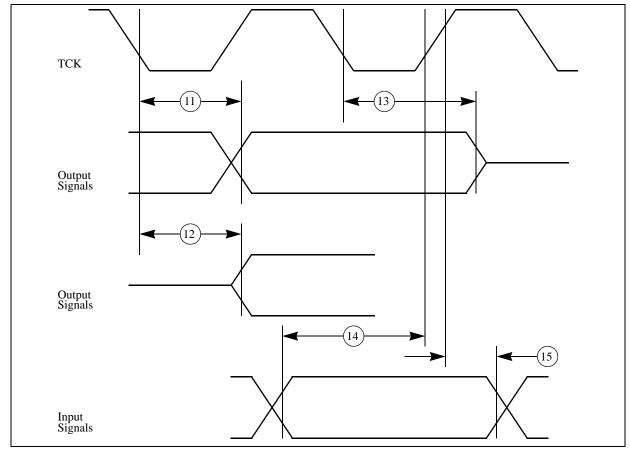

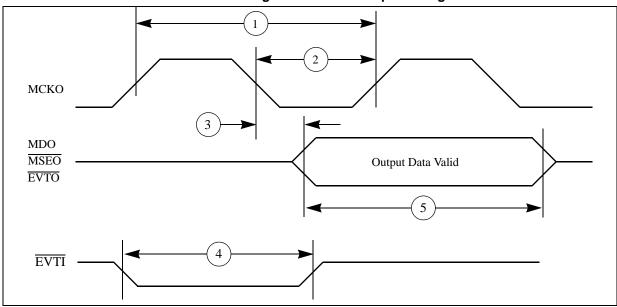

|   | 3.20 |                  | ing characteristics                        |     |

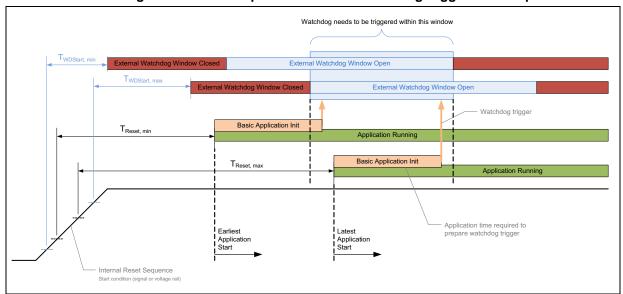

|   |      | 3.19.5           | External watchdog window                   |     |

|   |      | 3.19.4           | Reset sequence — start condition           |     |

|   |      | 3.19.3           | Reset sequence trigger mapping             |     |

|   |      | 3.19.2           | Reset sequence description                 |     |

|   |      | 3.19.1           | Reset sequence duration                    | 102 |

|   | 3.19 | Resets           | sequence                                   | 102 |

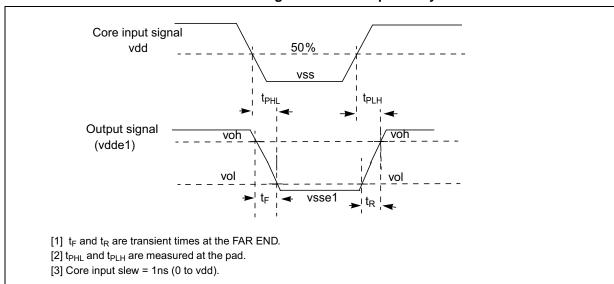

|   |      | 3.18.1           | Pad AC specifications                      | 101 |

|   | 3.18 | AC spe           | ecifications                               | 101 |

|   | 3.17 | SWG e            | electrical characteristics                 | 101 |

|   | 3.16 | Flash r          | memory electrical characteristics          | 99  |

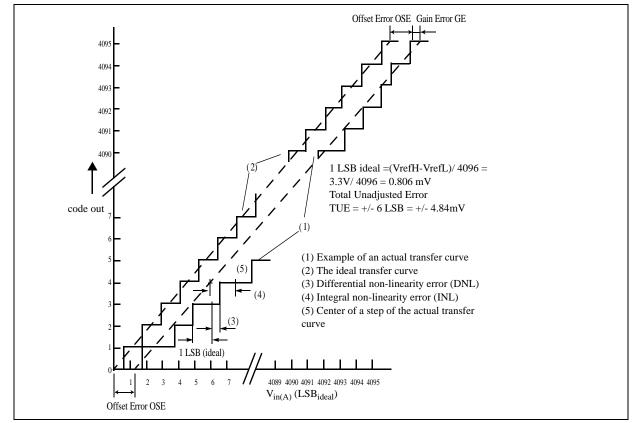

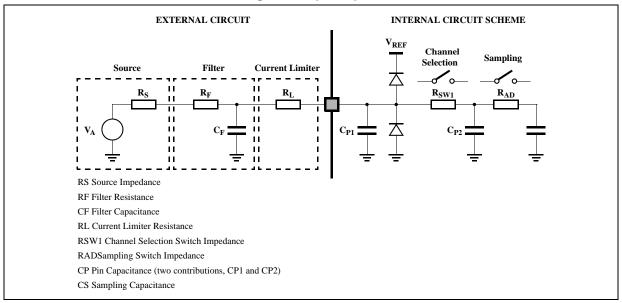

|   |      | 3.15.1           | Input Impedance and ADC Accuracy           | 94  |

|   | 3.15 | ADC el           | lectrical characteristics                  | 93  |

|   | 3.14 | 16 MH:           | z RC oscillator electrical characteristics | 93  |

|   | 3.13 | FMPLL            | electrical characteristics                 | 92  |

|   | 0.40 |                  | alactrical abaractaristics                 | 4   |

## List of tables

| Table 1.  | SPC56XL70/SPC56X64 device summary                        | 8    |

|-----------|----------------------------------------------------------|------|

| Table 2.  | Platform memory access time summary                      |      |

| Table 3.  | LQFP100 pin function summary                             | . 34 |

| Table 4.  | LQFP144 pin function summary                             | . 42 |

| Table 5.  | Supply pins                                              | . 54 |

| Table 6.  | System pins                                              | . 56 |

| Table 7.  | Pin muxing                                               | . 57 |

| Table 8.  | Absolute maximum ratings                                 | . 74 |

| Table 9.  | Recommended operating conditions (3.3 V)                 | . 75 |

| Table 10. | Decoupling capacitors                                    |      |

| Table 11. | Thermal characteristics for LQFP100 package              |      |

| Table 12. | Thermal characteristics for LQFP144 package              |      |

| Table 13. | EMI configuration summary                                |      |

| Table 14. | EMI emission testing specifications                      |      |

| Table 15. | ESD ratings                                              |      |

| Table 16. | Latch-up results                                         |      |

| Table 17. | Recommended operating characteristics                    | . 83 |

| Table 18. | Voltage regulator electrical specifications              |      |

| Table 19. | DC electrical characteristics                            |      |

| Table 20. | Current consumption characteristics                      |      |

| Table 21. | Temperature sensor electrical characteristics            |      |

| Table 22. | Main oscillator electrical characteristics               | . 91 |

| Table 23. | FMPLL electrical characteristics                         | . 92 |

| Table 24. | RC oscillator electrical characteristics                 | . 93 |

| Table 25. | ADC conversion characteristics                           | . 98 |

| Table 26. | Flash memory program and erase electrical specifications |      |

| Table 27. | Flash memory timing                                      | . 99 |

| Table 28. | Flash memory module life                                 | 100  |

| Table 29. | SPC56XL70 SWG Specifications                             | 101  |

| Table 30. | Pad AC specifications (3.3 V, IPP_HVE = 0)               | 101  |

| Table 31. | RESET sequences                                          | 103  |

| Table 32. | Reset sequence trigger — Reset sequence                  | 105  |

| Table 33. | Voltage thresholds                                       |      |

| Table 34. | RESET electrical characteristics                         | 109  |

| Table 35. | WKUP/NMI glitch filter                                   | 110  |

| Table 36. | JTAG pin AC electrical characteristics                   | 110  |

| Table 37. | Nexus debug port timing                                  | 112  |

| Table 38. | External interrupt timing                                | 114  |

| Table 39. | DSPI timing.                                             | 115  |

| Table 40. | LQFP100 mechanical data                                  | 122  |

| Table 41. | LQFP144 mechanical data                                  | 123  |

| Table 42. | Revision history                                         | 126  |

## List of figures

| Figure 1.  | SPC56EL70 block diagram                                    |     |

|------------|------------------------------------------------------------|-----|

| Figure 2.  | SPC56XL70 LQFP100 package                                  |     |

| Figure 3.  | SPC56XL70 LQFP144 pinout (top view)                        |     |

| Figure 4.  | Decoupling capacitors                                      |     |

| Figure 5.  | BCP68 board schematic example                              |     |

| Figure 6.  | Crystal oscillator and resonator connection scheme         |     |

| Figure 7.  | Main oscillator electrical characteristics                 |     |

| Figure 8.  | ADC characteristics and error definitions                  |     |

| Figure 9.  | Input Equivalent Circuit                                   |     |

| Figure 10. | Transient Behavior during Sampling Phase                   |     |

| Figure 11. | Spectral representation of input signal                    | 97  |

| Figure 12. | Pad output delay                                           |     |

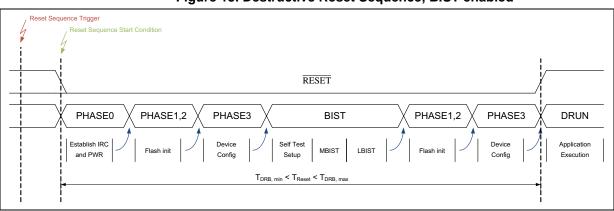

| Figure 13. | Destructive Reset Sequence, BIST enabled                   |     |

| Figure 14. | Destructive Reset Sequence, BIST disabled                  |     |

| Figure 15. | External Reset Sequence Long, BIST enabled                 |     |

| Figure 16. | Functional Reset Sequence Long                             |     |

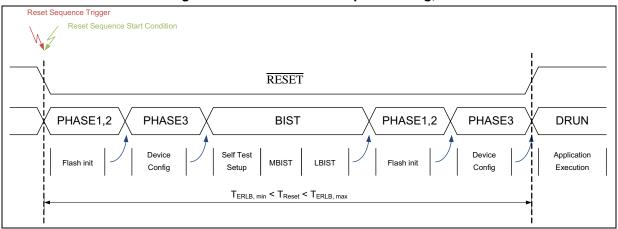

| Figure 17. | Functional Reset Sequence Short                            |     |

| Figure 18. | Reset sequence start for destructive resets                |     |

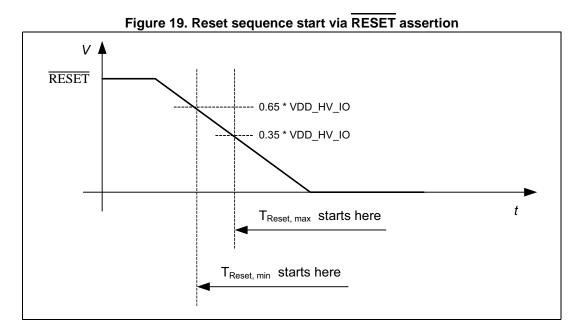

| Figure 19. | Reset sequence start via RESET assertion                   |     |

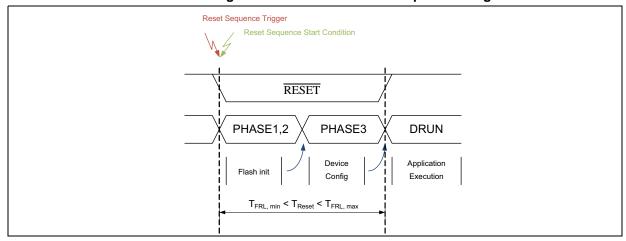

| Figure 20. | Reset sequence - External watchdog trigger window position |     |

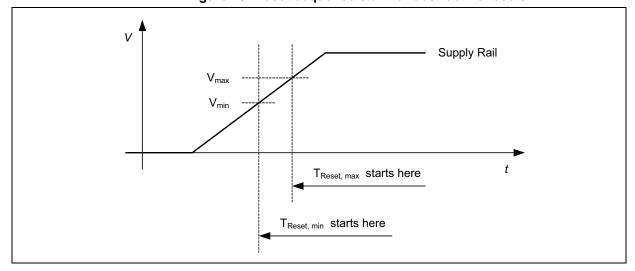

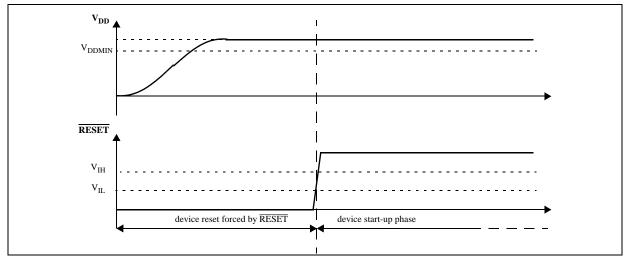

| Figure 21. | Start-up reset requirements                                |     |

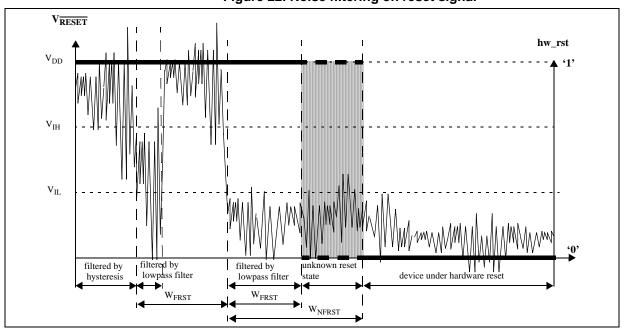

| Figure 22. | Noise filtering on reset signal                            |     |

| Figure 23. | JTAG test clock input timing                               |     |

| Figure 24. | JTAG test access port timing                               |     |

| Figure 25. | JTAG boundary scan timing                                  |     |

| Figure 26. | Nexus output timing                                        |     |

| Figure 27. | Nexus DDR Mode output timing                               |     |

| Figure 28. | Nexus TDI, TMS, TDO timing                                 |     |

| Figure 29. | External interrupt timing                                  |     |

| Figure 30. | DSPI classic SPI timing — master, CPHA = 0                 |     |

| Figure 31. | DSPI classic SPI timing — master, CPHA = 1                 |     |

| Figure 32. | DSPI classic SPI timing — slave, CPHA = 0                  |     |

| Figure 33. | DSPI classic SPI timing — slave, CPHA = 1                  |     |

| Figure 34. | DSPI modified transfer format timing — master, CPHA = 0    |     |

| Figure 35. | DSPI modified transfer format timing — master, CPHA = 1    |     |

| Figure 36. | DSPI modified transfer format timing – slave, CPHA = 0     |     |

| Figure 37. | DSPI modified transfer format timing — slave, CPHA = 1     |     |

| Figure 38. | DSPI PCS strobe (PCSS) timing                              |     |

| Figure 39. | LQFP100 package mechanical drawing                         |     |

| Figure 40. | LQFP144 package mechanical drawing                         |     |

| Figure 41  | Commercial product code structure                          | 125 |

#### 1 Introduction

#### 1.1 Document overview

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the devices.

This document provides electrical specifications, pin assignments, and package diagrams for the SPC56EL70x/SPC564L70x series of microcontroller units (MCUs). For functional characteristics, see the SPC56XL70 Microcontroller Reference Manual. For use of the SPC56XL70 in a fail-safe system according to safety standard ISO26262, see the Safety Application Guide for SPCEL70.

#### 1.2 Description

The SPC56EL70x/SPC564L70x series microcontrollers are system-on-chip devices that are built on Power Architecture technology and contain enhancements that improve the architecture's fit in embedded applications, include additional instruction support for digital signal processing (DSP) and integrate technologies such as an enhanced time processor unit, enhanced queued analog-to-digital converter, Controller Area Network, and an enhanced modular input-output system.

The SPC56EL70x/SPC564L70x family of 32-bit microcontrollers is the latest achievement in integrated automotive application controllers. It belongs to an expanding range of automotive-focused products designed to address electrical hydraulic power steering (EHPS), electric power steering (EPS) and airbag applications. The advanced and cost-efficient host processor core of the SPC56XL70 automotive controller family complies with the Power Architecture embedded category. It operates at speeds as high as 120 MHz and offers high-performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users' implementations.

## 1.3 Device comparison

Table 1. SPC56XL70/SPC56X64 device summary

| Feature    |                                                                               | SPC56EL64                                                 | SPC56EL70                                                 | SPC564L64          | SPC564L70      |  |

|------------|-------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|--------------------|----------------|--|

|            | Туре                                                                          | 2 × e200z4<br>(in lock-step or<br>decoupled<br>operation) | 2 × e200z4<br>(in lock-step or<br>decoupled<br>operation) | 1 × e200z4         | 1 × e200z4     |  |

|            | Architecture                                                                  |                                                           | На                                                        | rvard              |                |  |

|            | Execution speed                                                               |                                                           | 0–120 MF                                                  | Hz (+2% FM)        |                |  |

|            | DMIPS intrinsic performance                                                   |                                                           | >240                                                      | ) MIPS             |                |  |

|            | SIMD<br>(DSP + FPU)                                                           |                                                           | ,                                                         | Yes                |                |  |

| CPU        | MMU                                                                           |                                                           | 16                                                        | entry              |                |  |

|            | Instruction set PPC                                                           | Yes                                                       |                                                           |                    |                |  |

|            | Instruction set VLE                                                           | Yes                                                       |                                                           |                    |                |  |

|            | Instruction cache                                                             | 4 KB, EDC                                                 |                                                           |                    |                |  |

|            | MPU-16 regions                                                                | Yes, replicated module                                    |                                                           |                    |                |  |

|            | Semaphore unit (SEMA4)                                                        | Yes                                                       |                                                           |                    |                |  |

|            | Core bus                                                                      |                                                           | AHB, 32-bit ad                                            | dress, 64-bit data |                |  |

| Buses      | Internal periphery bus                                                        | 32-bit address, 32-bit data                               |                                                           |                    |                |  |

| Crossbar   | Dar Master × slave ports Lock Step Mode: 4 × 3 Decoupled Parallel Mode: 6 × 3 |                                                           | 4 >                                                       | (3                 |                |  |

| Memory     | Code/data flash                                                               | 1.5 MB, ECC,<br>RWW                                       | 2 MB, ECC, RWW                                            | 1.5 MB, ECC, RWW   | 2 MB, ECC, RWW |  |

| iviciliory | Static RAM<br>(SRAM)                                                          | 160 KB, ECC                                               | 192 KB, ECC                                               | 160 KB, ECC        | 192 KB, ECC    |  |

Table 1. SPC56XL70/SPC56X64 device summary (continued)

| 1       | Feature                                           | SPC56EL64                                                                 | SPC56EL70              | SPC564L64                      | SPC564L70 |  |

|---------|---------------------------------------------------|---------------------------------------------------------------------------|------------------------|--------------------------------|-----------|--|

|         | Interrupt<br>Controller<br>(INTC)                 | 16 interrupt levels, replicated module                                    |                        |                                |           |  |

|         | Periodic<br>Interrupt Timer<br>(PIT)              |                                                                           | 1 × 4                  | channels                       |           |  |

|         | System Timer<br>Module (STM)                      |                                                                           | 1 × 4 channels,        | replicated module              |           |  |

|         | Software<br>Watchdog<br>Timer (SWT)               | Yes, replicated module                                                    |                        |                                |           |  |

|         | eDMA                                              |                                                                           | 16 channels, r         | eplicated module               |           |  |

|         | FlexRay                                           | 1 × 64 message buffers, dual channel                                      |                        |                                |           |  |

|         | FlexCAN                                           |                                                                           | 3 × 32 message buffers |                                |           |  |

| Modules | LINFlexD<br>(UART and LIN<br>with DMA<br>support) | 2                                                                         |                        |                                |           |  |

|         | Clock out                                         |                                                                           | ,                      | Yes                            |           |  |

|         | Fault Collection<br>and Control<br>Unit (FCCU)    | Yes                                                                       |                        |                                |           |  |

|         | Cross<br>Triggering Unit<br>(CTU)                 |                                                                           | ,                      | Yes                            |           |  |

|         | eTimer                                            |                                                                           | 3 × 6 c                | hannels <sup>(1)</sup>         |           |  |

|         | FlexPWM                                           |                                                                           | 2 Module 4 × (         | 2 + 1) channels <sup>(2)</sup> |           |  |

|         | Analog-to-<br>Digital<br>Converter<br>(ADC)       | 2 × 12-bit ADC, 16 channels per ADC (3 internal, 4 shared and 9 external) |                        |                                |           |  |

|         | Sine Wave<br>Generator<br>(SWG)                   |                                                                           | 32                     | point                          |           |  |

Table 1. SPC56XL70/SPC56X64 device summary (continued)

| Feature            |                                                                                   | SPC56EL64                                                                                               | SPC56EL70 | SPC564L64 | SPC564L70 |  |  |  |

|--------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|--|--|--|

|                    | Deserial Serial<br>Peripheral<br>Interface (DSPI)                                 | 3 × DSPI as many as 8 chip selects                                                                      |           |           |           |  |  |  |

| Modules<br>(cont.) | Cyclic<br>Redundancy<br>Checker (CRC)<br>unit                                     |                                                                                                         | Yes       |           |           |  |  |  |

|                    | Junction<br>temperature<br>sensor<br>(TSENS)                                      | Yes, replicated module                                                                                  |           |           |           |  |  |  |

|                    | Digital I/Os                                                                      |                                                                                                         |           | ≥ 16      |           |  |  |  |

|                    | Device power supply                                                               | 3.3 V with integrated bypassable ballast transistor External ballast transistor not needed for bare die |           |           |           |  |  |  |

| Supply             | Analog<br>reference<br>voltage                                                    | 3.0 V – 3.6 V and 4.5 V – 5.5 V                                                                         |           |           |           |  |  |  |

|                    | Frequency-<br>modulated<br>phase-locked<br>loop (FMPLL)                           | 2                                                                                                       |           |           |           |  |  |  |

| Clocking           | Internal RC oscillator                                                            | 16 MHz                                                                                                  |           |           |           |  |  |  |

|                    | External crystal oscillator                                                       | 4 – 40 MHz                                                                                              |           |           |           |  |  |  |

| Debug              | Nexus                                                                             |                                                                                                         | Le        | vel 3+    |           |  |  |  |

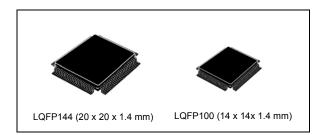

| Package<br>s       | LQFP                                                                              | 100 pins<br>144 pins                                                                                    |           |           |           |  |  |  |

|                    | Temperature range (junction)                                                      | $-40$ to 150 $^{\circ}$ C                                                                               |           |           |           |  |  |  |

| Temperat<br>ure    | Ambient<br>temperature<br>range using<br>external ballast<br>transistor<br>(LQFP) | −40 to 125 °C                                                                                           |           |           |           |  |  |  |

<sup>1.</sup> The third eTimer is not connected to any pins on the package. Its usage is confined internally to the device.

57/

<sup>2.</sup> The second FlexPWM is not connected to any pins on the package. Its usage is confined internally to the device.

#### 1.4 Block diagram

Figure 1 shows a top-level block diagram of the SPC56EL70x/SPC564L70x device.

**PMU** JTAG e200z4 e200z4 Nexus SWT SWT ECSM **ECSM** SPE SPE STM STM **VLE VLE** INTC INTC MMU MMU SEMA4 FlexRay SEMA4 I-CACHE I-CACHE eDMA RCeDMA Crossbar Switch Crossbar Switch Memory Protection Unit Memory Protection Unit ECC logic for SRAM ECC logic for SRAM PBRIDGE **PBRIDGE** RC RC TSENS TSENS Flash memory **SRAM** ECC bits ECC bits + logic RC CMU - LIN controller with DMA support ADC - Analog-to-Digital Converter LINFlexD BAM - Boot Assist Module MC Mode Entry, Clock, Reset, & Power PBRIDGE - Peripheral bridge CMU - Clock Monitoring Unit CRC - Cyclic Redundancy Check unit PIT - Periodic Interrupt Timer CTU- Cross Triggering Unit **PMU** - Power Management Unit **DSPI** - Serial Peripherals Interface RC - Redundancy Checker - Error Correction Code RTC - Real Time Clock **ECC ECSM** SEMA4 - Error Correction Status Module - Semaphore Unit eDMA - Enhanced Direct Memory Access controller SIUL - System Integration Unit Lite **FCCU** - Fault Collection and Control Unit SSCM - System Status and Configuration Module FlexCAN - Controller Area Network controller STM - System Timer Module **FMPLL** - Frequency Modulated Phase Locked Loop **SWG** - Sine Wave Generator INTC - Interrupt Controller SWT - Software Watchdog Timer **IRCOSC** - Internal RC Oscillator **TSENS** - Temperature Sensor **JTAG** - Joint Test Action Group interface XOSC - Crystal Oscillator

Figure 1. SPC56EL70 block diagram

DocID023953 Rev 5

#### 1.5 Feature details

#### 1.5.1 High-performance e200z4d core

The e200z4d Power Architecture® core provides the following features:

- 2 independent execution units, both supporting fixed-point and floating-point operations

- Dual issue 32-bit Power Architecture technology compliant

- 5-stage pipeline (IF, DEC, EX1, EX2, WB)

- In-order execution and instruction retirement

- Full support for Power Architecture instruction set and Variable Length Encoding (VLE)

- Mix of classic 32-bit and 16-bit instruction allowed

- Optimization of code size possible

- Thirty-two 64-bit general purpose registers (GPRs)

- Harvard bus (32-bit address, 64-bit data)

- I-Bus interface capable of one outstanding transaction plus one piped with no waiton-data return

- D-Bus interface capable of two transactions outstanding to fill AHB pipe

- I-cache and I-cache controller

- 4 KB, 256-bit cache line (programmable for 2- or 4-way)

- No data cache

- 16-entry MMU

- 8-entry branch table buffer

- Branch look-ahead instruction buffer to accelerate branching

- Dedicated branch address calculator

- 3 cycles worst case for missed branch

- Load/store unit

- Fully pipelined

- Single-cycle load latency

- Big- and little-endian modes supported

- Misaligned access support

- Single stall cycle on load to use

- Single-cycle throughput (2-cycle latency) integer 32 × 32 multiplication

- 4 14 cycles integer 32 × 32 division (average division on various benchmark of nine cycles)

- Single precision floating-point unit

- 1 cycle throughput (2-cycle latency) floating-point 32 × 32 multiplication

- Target 9 cycles (worst case acceptable is 12 cycles) throughput floating-point 32 × 32 division

- Special square root and min/max function implemented

- Signal processing support: APU-SPE 1.1

- Support for vectorized mode: as many as two floating-point instructions per clock

- Vectored interrupt support

- Reservation instruction to support read-modify-write constructs

Extensive system development and tracing support via Nexus debug port

#### 1.5.2 Crossbar switch (XBAR)

The XBAR multi-port crossbar switch supports simultaneous connections between four master ports and three slave ports. The crossbar supports a 32-bit address bus width and a 64-bit data bus width.

The crossbar allows four concurrent transactions to occur from any master port to any slave port, although one of those transfers must be an instruction fetch from internal flash memory. If a slave port is simultaneously requested by more than one master port, arbitration logic selects the higher priority master and grants it ownership of the slave port. All other masters requesting that slave port are stalled until the higher priority master completes its transactions.

The crossbar provides the following features:

- 4 masters and 3 slaves supported per each replicated crossbar

- Masters allocation for each crossbar: e200z4d core with two independent bus interface units (BIU) for I and D access (2 masters), one eDMA, one FlexRay

- Slaves allocation for each crossbar: a redundant flash-memory controller with 2 slave ports to guarantee maximum flexibility to handle Instruction and Data array, one redundant SRAM controller with 1 slave port each and 1 redundant peripheral bus bridge

- 32-bit address bus and 64-bit data bus

- Programmable arbitration priority

- Requesting masters can be treated with equal priority and are granted access to a slave port in round-robin method, based upon the ID of the last master to be granted access or a priority order can be assigned by software at application run time

- Temporary dynamic priority elevation of masters

The XBAR is replicated for each processing channel.

#### 1.5.3 Memory protection unit (MPU)

The Memory Protection Unit splits the physical memory into 16 different regions. Each master (eDMA, FlexRay, CPU) can be assigned different access rights to each region.

- 16-region MPU with concurrent checks against each master access

- 32-byte granularity for protected address region

The memory protection unit is replicated for each processing channel.

#### 1.5.4 Enhanced direct memory access (eDMA)

The enhanced direct memory access (eDMA) controller is a second-generation module capable of performing complex data movements via 16 programmable channels, with minimal intervention from the host processor. The hardware micro architecture includes a DMA engine which performs source and destination address calculations, and the actual data movement operations, along with an SRAM-based memory containing the transfer control descriptors (TCD) for the channels. This implementation is used to minimize the overall block size.

DocID023953 Rev 5

13/128

The eDMA module provides the following features:

- 16 channels supporting 8-, 16-, and 32-bit value single or block transfers

- Support variable sized queues and circular buffered queue

- Source and destination address registers independently configured to post-increment or stay constant

- Support major and minor loop offset

- Support minor and major loop done signals

- DMA task initiated either by hardware requestor or by software

- Each DMA task can optionally generate an interrupt at completion and retirement of the task

- Signal to indicate closure of last minor loop

- Transfer control descriptors mapped inside the SRAM

The eDMA controller is replicated for each processing channel.

#### 1.5.5 On-chip flash memory with ECC

This device includes programmable, non-volatile flash memory. The non-volatile memory (NVM) can be used for instruction storage or data storage, or both. The flash memory module interfaces with the system bus through a dedicated flash memory array controller. It supports a 64-bit data bus width at the system bus port, and a 128-bit read data interface to flash memory. The module contains four 128-bit prefetch buffers. Prefetch buffer hits allow no-wait responses. Buffer misses incur a 3 wait state response at 120 MHz.

The flash memory module provides the following features:

- 2 MB of flash memory in unique multi-partitioned hard macro

- Sectorization:

- Partition 1 (low address): 16 KB + 16 KB + 16 KB + 16 KB

- Partition 2 (low address): 16 KB + 16 KB + 16 KB + 16 KB

- Partition 3 (low address): 64 KB + 64 KB

- Partition 4 (mid address): 128 KB + 128 KB

- Partition 5 (high address): 256 KB + 256 KB

- Partition 6 (high address): 256 KB + 256 KB

- Partition 7 (high address): 256 KB + 256 KB

- EEPROM emulation (in software) within same module but on different partition

- 16 KB test sector and 16 KB shadow sector for test, censorship device and user option bits

- Wait states:

- Access time less or equal to 3 WS at 120 MHz + 4% FM (4-1-2-1 access)

- Access time less or equal to 2 WS at 80 MHz + 4% FM

- Flash memory line 128-bit wide with 8-bit ECC on 64-bit word (total 144 bits)

- Accessed via a 64-bit wide bus for write and a 128-bit wide array for read operations

- 1-bit error correction, 2-bit error detection

#### 1.5.6 On-chip SRAM with ECC

The SPC56XL70 SRAM provides a general-purpose single port memory.

ECC handling is done on a 32-bit boundary for data and it is extended to the address to have the highest possible diagnostic coverage including the array internal address decoder.

The SRAM module provides the following features:

- System SRAM: 192 KB

- ECC on 32-bit word (syndrome of 7 bits)

- ECC covers SRAM bus address

- 1-bit error correction, 2-bit error detection

- Wait states:

- 1 wait state at 120 MHz

- 0 wait states at 80 MHz

#### 1.5.7 Platform flash memory controller

The following list summarizes the key features of the flash memory controller:

- Single AHB port interface supports a 64-bit data bus. All AHB aligned and unaligned reads within the 32-bit container are supported. Only aligned word writes are supported.

- Array interfaces support a 128-bit read data bus and a 64-bit write data bus for each bank.

- Code flash (bank0) interface provides configurable read buffering and page prefetch support.

- Four page-read buffers (each 128 bits wide) and a prefetch controller support speculative reading and optimized flash access.

- Single-cycle read responses (0 AHB data-phase wait states) for hits in the buffers. The buffers implement a least-recently-used replacement algorithm to maximize performance.

- Data flash (bank1) interface includes a 128-bit register to temporarily hold a single flash page. This logic supports single-cycle read responses (0 AHB data-phase wait states) for accesses that hit in the holding register.

- No prefetch support is provided for this bank.

- Programmable response for read-while-write sequences including support for stallwhile-write, optional stall notification interrupt, optional flash operation abort and optional abort notification interrupt.

- Separate and independent configurable access timing (on a per bank basis) to support use across a wide range of platforms and frequencies.

- Support of address-based read access timing for emulation of other memory types.

- Support for reporting of single- and multi-bit error events.

- Typical operating configuration loaded into programming model by system reset.

The platform flash controller is replicated for each processor.

#### 1.5.8 Platform static RAM controller (SRAMC)

The SRAMC module is the platform SRAM array controller, with integrated error detection and correction.

DocID023953 Rev 5

15/128

The main features of the SRAMC provide connectivity for the following interfaces:

- XBAR Slave Port (64-bit data path)

- ECSM (ECC Error Reporting, error injection and configuration)

- SRAM array

The following functions are implemented:

- ECC encoding (32-bit boundary for data and complete address bus)

- ECC decoding (32-bit boundary and entire address)

- Address translation from the AHB protocol on the XBAR to the SRAM array

The platform SRAM controller is replicated for each processor.

#### 1.5.9 Memory subsystem access time

Every memory access the CPU performs requires at least one system clock cycle for the data phase of the access. Slower memories or peripherals may require additional data phase wait states. Additional data phase wait states may also occur if the slave being accessed is not parked on the requesting master in the crossbar.

*Table 2* shows the number of additional data phase wait states required for a range of memory accesses.

| AHB transfer                                                                                               | Data phase wait states | Description                                                                                                     |

|------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------|

| e200z4d instruction fetch                                                                                  | 0                      | Flash memory prefetch buffer hit (page hit)                                                                     |

| e200z4d instruction fetch  3 Flash memory prefetch buffer miss (based on 4-cycle random flash array access |                        | Flash memory prefetch buffer miss (based on 4-cycle random flash array access time)                             |

| e200z4d data read                                                                                          | 0–1                    | SRAM read                                                                                                       |

| e200z4d data write                                                                                         | 0                      | SRAM 32-bit write                                                                                               |

| e200z4d data write                                                                                         | 0                      | SRAM 64-bit write (executed as 2 x 32-bit writes)                                                               |

| e200z4d data write                                                                                         | 0–2                    | SRAM 8-,16-bit write (Read-modify-Write for ECC)                                                                |

| e200z4d flash memory read                                                                                  | 0                      | Flash memory prefetch buffer hit (page hit)                                                                     |

| e200z4d flash memory read                                                                                  | 3                      | Flash memory prefetch buffer miss (at 120 MHz; includes 1 cycle of program flash memory controller arbitration) |

Table 2. Platform memory access time summary

#### 1.5.10 Error correction status module (ECSM)

The ECSM on this device manages the ECC configuration and reporting for the platform memories (flash memory and SRAM). It does not implement the actual ECC calculation. A detected error (double error for flash memory or SRAM) is also reported to the FCCU. The following errors and indications are reported into the ECSM dedicated registers:

- ECC error status and configuration for flash memory and SRAM

- ECC error reporting for flash memory

- ECC error reporting for SRAM

- ECC error injection for SRAM

#### 1.5.11 Peripheral bridge (PBRIDGE)

The PBRIDGE implements the following features:

- Duplicated periphery

- Master access right per peripheral (per master: read access enable; write access enable)

- Checker applied on PBRIDGE output toward periphery

- Byte endianess swap capability

#### 1.5.12 Interrupt controller (INTC)

The INTC provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems.

For high-priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR needs to be executed. It also provides an ample number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

The INTC supports the priority ceiling protocol for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the resource can not preempt each other.

The INTC provides the following features:

- Duplicated periphery

- Unique 9-bit vector per interrupt source

- 16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

- Priority elevation for shared resource

The INTC is replicated for each processor.

#### 1.5.13 System clocks and clock generation

The following list summarizes the system clock and clock generation on this device:

- Lock status continuously monitored by lock detect circuitry

- Loss-of-clock (LOC) detection for reference and feedback clocks

- On-chip loop filter (for improved electromagnetic interference performance and fewer external components required)

- Programmable output clock divider of system clock (÷1, ÷2, ÷4, ÷8)

- FlexPWM module and as many as three eTimer modules running on an auxiliary clock independent from system clock (with max frequency 120 MHz)

- On-chip crystal oscillator with automatic level control

- Dedicated internal 16 MHz internal RC oscillator for rapid start-up

- Supports automated frequency trimming by hardware during device startup and by user application

- Auxiliary clock domain for motor control periphery (FlexPWM, eTimer, CTU, ADC, and SWG)

#### 1.5.14 Frequency-Modulated Phase-Locked Loop (FMPLL)

Each device has two FMPLLs.

Each FMPLL allows the user to generate high speed system clocks starting from a minimum reference of 4 MHz input clock. Further, the FMPLL supports programmable frequency modulation of the system clock. The FMPLL multiplication factor, output clock divider ratio are all software configurable. The FMPLLs have the following major features:

- Input frequency: 4–40 MHz continuous range (limited by the crystal oscillator)

- Voltage controlled oscillator (VCO) range: 256–512 MHz

- Frequency modulation via software control to reduce and control emission peaks

- Modulation depth ±2% if centered or 0% to –4% if downshifted via software control register

- Modulation frequency: triangular modulation with 25 KHz nominal rate

- Option to switch modulation on and off via software interface

- Reduced frequency divider (RFD) for reduced frequency operation without re-lock

- 3 modes of operation

- Bypass mode

- Normal FMPLL mode with crystal reference (default)

- Normal FMPLL mode with external reference

- Lock monitor circuitry with lock status

- Loss-of-lock detection for reference and feedback clocks

- Self-clocked mode (SCM) operation

- On-chip loop filter

- Auxiliary FMPLL

- Used for FlexRay due to precise symbol rate requirement by the protocol

- Used for motor control periphery and connected IP (A/D digital interface CTU) to allow independent frequencies of operation for PWM and timers and jitter-free control

- Option to enable/disable modulation to avoid protocol violation on jitter and/or potential unadjusted error in electric motor control loop

- Allows to run motor control periphery at different (precisely lower, equal or higher as required) frequency than the system to ensure higher resolution

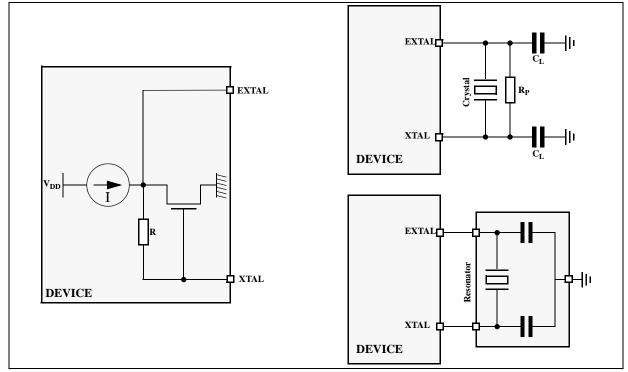

#### 1.5.15 Main oscillator

The main oscillator provides these features:

- Input frequency range 4–40 MHz

- Crystal input mode

- External reference clock (3.3 V) input mode

- FMPLL reference

#### 1.5.16 Internal reference clock (RC) oscillator

The architecture uses constant current charging of a capacitor. The voltage at the capacitor is compared to the stable bandgap reference voltage. The RC oscillator is the device safe clock.

The RC oscillator provides these features:

- Nominal frequency 16 MHz

- ±5% variation over voltage and temperature after process trim

- Clock output of the RC oscillator serves as system clock source in case loss of lock or loss of clock is detected by the FMPLL

- RC oscillator is used as the default system clock during startup and can be used as back-up input source of FMPLL(s) in case XOSC fails

## 1.5.17 Clock, reset, power, mode and test control modules (MC\_CGM, MC\_RGM, MC\_PCU, and MC\_ME)

These modules provide the following:

- Clock gating and clock distribution control

- Halt, stop mode control

- Flexible configurable system and auxiliary clock dividers

- Various execution modes

- HALT and STOP mode as reduced activity low power mode

- Reset, Idle, Test, Safe

- Various RUN modes with software selectable powered modules

- No stand-by mode implemented (no internal switchable power domains)

#### 1.5.18 Periodic interrupt timer module (PIT)

The PIT module implements the following features:

- 4 general purpose interrupt timers

- 32-bit counter resolution

- Can be used for software tick or DMA trigger operation

DocID023953 Rev 5

19/128

#### 1.5.19 System timer module (STM)

The STM implements the following features:

- Up-counter with 4 output compare registers

- OS task protection and hardware tick implementation per AUTOSAR<sup>(a)</sup> requirement

The STM is replicated for each processor.

#### 1.5.20 Software watchdog timer (SWT)

This module implements the following features:

- Fault tolerant output

- Safe internal RC oscillator as reference clock

- Windowed watchdog

- Program flow control monitor with 16-bit pseudorandom key generation

- Allows a high level of safety (SIL3 monitor)

The SWT module is replicated for each processor.

#### 1.5.21 Fault collection and control unit (FCCU)

The FCCU module has the following features:

- · Redundant collection of hardware checker results

- Redundant collection of error information and latch of faults from critical modules on the device

- Collection of self-test results

- Configurable and graded fault control

- Internal reactions (no internal reaction, IRQ, Functional Reset, Destructive Reset, or Safe mode entered)

- External reaction (failure is reported to the external/surrounding system via configurable output pins)

#### 1.5.22 System Integration Unit Lite (SIUL)

The SIUL controls MCU reset configuration, pad configuration, external interrupt, general purpose I/O (GPIO), internal peripheral multiplexing, and system reset operation. The reset configuration block contains the external pin boot configuration logic. The pad configuration block controls the static electrical characteristics of I/O pins. The GPIO block provides uniform and discrete input/output control of the I/O pins of the MCU.

a. Automotive Open System Architecture

The SIU provides the following features:

- Centralized pad control on a per-pin basis

- Pin function selection

- Configurable weak pull-up/down

- Configurable slew rate control (slow/medium/fast)

- Hysteresis on GPIO pins

- Configurable automatic safe mode pad control

- Input filtering for external interrupts

#### 1.5.23 Non-maskable interrupt (NMI)

The non-maskable interrupt with de-glitching filter supports high-priority core exceptions.

#### 1.5.24 Boot assist module (BAM)

The BAM is a block of read-only memory with hard-coded content. The BAM program is executed only if serial booting mode is selected via boot configuration pins.

The BAM provides the following features:

- Enables booting via serial mode (FlexCAN or LINFlex-UART)

- Supports programmable 64-bit password protection for serial boot mode

- Supports serial bootloading of either Power Architecture code (default) or VLE code

- Automatic switch to serial boot mode if internal flash memory is blank or invalid

#### 1.5.25 System status and configuration module (SSCM)

The SSCM on this device features the following:

- System configuration and status

- Debug port status and debug port enable

- Multiple boot code starting locations out of reset through implementation of search for valid Reset Configuration Half Word

- Sets up the MMU to allow user boot code to execute as either Power Architecture code (default) or as VLE code out of flash memory

- Triggering of device self-tests during reset phase of device boot

#### 1.5.26 FlexCAN

The FlexCAN module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to be used primarily as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness and required bandwidth.

The FlexCAN module provides the following features:

- Full implementation of the CAN protocol specification, version 2.0B

- Standard data and remote frames

- Extended data and remote frames

- 0 to 8 bytes data length

- Programmable bit rate as fast as 1Mbit/s

- 32 message buffers of 0 to 8 bytes data length

- Each message buffer configurable as receive or transmit buffer, all supporting standard and extended messages

- Programmable loop-back mode supporting self-test operation

- 3 programmable mask registers

- Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independent of the transmission medium (an external transceiver is assumed)

- High immunity to EMI

- Short latency time due to an arbitration scheme for high-priority messages

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

- Receive features

- Individual programmable filters for each mailbox

- 8 mailboxes configurable as a 6-entry receive FIFO

- 8 programmable acceptance filters for receive FIFO

- Programmable clock source

- System clock

- Direct oscillator clock to avoid FMPLL jitter

5

#### 1.5.27 FlexRay

The FlexRay module provides the following features:

- Full implementation of FlexRay Protocol Specification 2.1 Rev. A

- 64 configurable message buffers can be handled

- Dual channel or single channel mode of operation, each as fast as 10 Mbit/s data rate

- Message buffers configurable as transmit or receive

- Message buffer size configurable

- Message filtering for all message buffers based on Frame ID, cycle count, and message ID

- Programmable acceptance filters for receive FIFO

- Message buffer header, status, and payload data stored in system memory (SRAM)

- Internal FlexRay memories have error detection and correction

#### 1.5.28 Serial communication interface module (LINFlexD)

The LINFlexD module (LINFlex with DMA support) on this device features the following:

- Supports LIN Master mode, LIN Slave mode and UART mode

- LIN state machine compliant to LIN1.3, 2.0, and 2.1 specifications

- Manages LIN frame transmission and reception without CPU intervention

- LIN features

- Autonomous LIN frame handling

- Message buffer to store as many as 8 data bytes

- Supports messages as long as 64 bytes

- Detection and flagging of LIN errors (Sync field, delimiter, ID parity, bit framing, checksum and Time-out errors)

- Classic or extended checksum calculation

- Configurable break duration of up to 50-bit times

- Programmable baud rate prescalers (13-bit mantissa, 4-bit fractional)

- Diagnostic features (Loop back, LIN bus stuck dominant detection)

- Interrupt driven operation with 16 interrupt sources

- LIN slave mode features

- Autonomous LIN header handling

- Autonomous LIN response handling

- UART mode

- Full-duplex operation

- Standard non return-to-zero (NRZ) mark/space format

- Data buffers with 4-byte receive, 4-byte transmit

- Configurable word length (8-bit, 9-bit, or 16-bit words)

- Configurable parity scheme: none, odd, even, always 0

- Speed as fast as 2 Mbit/s

- Error detection and flagging (Parity, Noise and Framing errors)

- Interrupt driven operation with four interrupt sources

- Separate transmitter and receiver CPU interrupt sources

- 16-bit programmable baud-rate modulus counter and 16-bit fractional

- 2 receiver wake-up methods

- Support for DMA enabled transfers

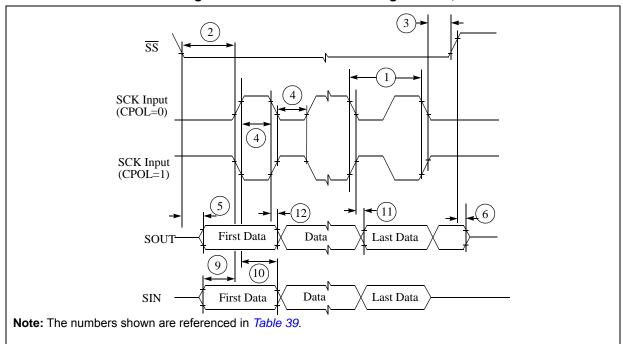

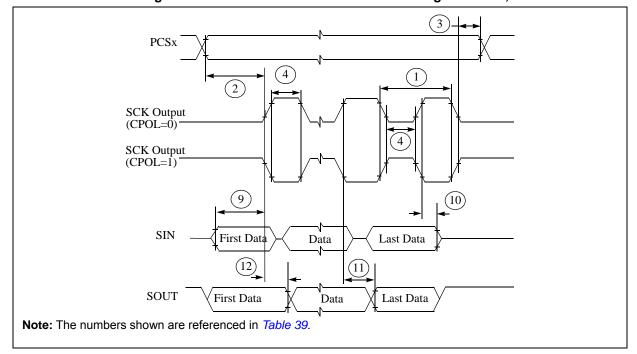

#### 1.5.29 Deserial serial peripheral interface (DSPI)

The DSPI modules provide a synchronous serial interface for communication between the SPC56XL70 and external devices.

A DSPI module provides these features:

- Full duplex, synchronous transfers

- Master or slave operation

- Programmable master bit rates

- Programmable clock polarity and phase

- End-of-transmission interrupt flag

- Programmable transfer baud rate

- Programmable data frames from 4 to 16 bits

- As many as 8 chip select lines available, depending on package and pin multiplexing

- 4 clock and transfer attributes registers

- Chip select strobe available as alternate function on one of the chip select pins for deglitching

- FIFOs for buffering as many as 5 transfers on the transmit and receive side

- Queueing operation possible through use of the eDMA

- General purpose I/O functionality on pins when not used for SPI

#### 1.5.30 FlexPWM

The pulse width modulator module (FlexPWM) contains four PWM channels, each of which is configured to control a single half-bridge power stage. One module is present in LQFP144 package. Additionally, four fault input channels are provided per FlexPWM module.

This PWM is capable of controlling most motor types, including:

- AC induction motors (ACIM)

- Permanent Magnet AC motors (PMAC)

- Brushless (BLDC) and brush DC motors (BDC)

- Switched (SRM) and variable reluctance motors (VRM)

- Stepper motors

A FlexPWM module implements the following features:

- 16 bits of resolution for center, edge aligned, and asymmetrical PWMs

- Maximum operating frequency as high as 120 MHz

- Clock source not modulated and independent from system clock (generated via secondary FMPLL)

- Fine granularity control for enhanced resolution of the PWM period

- PWM outputs can operate as complementary pairs or independent channels

- Ability to accept signed numbers for PWM generation

- Independent control of both edges of each PWM output

- Synchronization to external hardware or other PWM supported

- Double buffered PWM registers

- Integral reload rates from 1 to 16

- Half cycle reload capability

- Multiple ADC trigger events can be generated per PWM cycle via hardware

- Fault inputs can be assigned to control multiple PWM outputs

- Programmable filters for fault inputs

- Independently programmable PWM output polarity

- Independent top and bottom deadtime insertion

- Each complementary pair can operate with its own PWM frequency and deadtime values

- Individual software control for each PWM output

- All outputs can be forced to a value simultaneously

- PWMX pin can optionally output a third signal from each channel

- Channels not used for PWM generation can be used for buffered output compare functions

- Channels not used for PWM generation can be used for input capture functions

- Enhanced dual edge capture functionality

- Option to supply the source for each complementary PWM signal pair from any of the following:

- External digital pin

- Internal timer channel

- External ADC input, taking into account values set in ADC high- and low-limit registers

- DMA support

5//

#### 1.5.31 eTimer module

The SPC56XL70 provides two eTimer modules on the LQFP144 package. Six 16-bit general purpose up/down timer/counters per module are implemented with the following features:

- Maximum clock frequency of 120 MHz

- Individual channel capability

- Input capture trigger

- Output compare

- Double buffer (to capture rising edge and falling edge)

- Separate prescaler for each counter

- Selectable clock source

- 0–100% pulse measurement

- Rotation direction flag (Quad decoder mode)

- Maximum count rate

- Equals peripheral clock divided by 2 for external event counting

- Equals peripheral clock for internal clock counting

- Cascadeable counters

- Programmable count modulo

- · Quadrature decode capabilities

- Counters can share available input pins

- Count once or repeatedly

- · Preloadable counters

- Pins available as GPIO when timer functionality not in use

- DMA support

#### 1.5.32 Sine wave generator (SWG)

A digital-to-analog converter is available to generate a sine wave based on 32 stored values for external devices (ex: resolver).

- Frequency range from 1 KHz to 50 KHz

- Sine wave amplitude from 0.47 V to 2.26 V

#### 1.5.33 Analog-to-Digital converter module (ADC)

The ADC module features include:

#### Analog part:

- 2 on-chip ADCs

- 12-bit resolution SAR architecture

- Same digital interface as in the SPC560P family

- A/D Channels: 9 external, 3 internal and 4 shared with other A/D (total 16 channels)

- One channel dedicated to each T-sensor to enable temperature reading during application

- Separated reference for each ADC

- Shared analog supply voltage for both ADCs

- One sample and hold unit per ADC

- Adjustable sampling and conversion time

#### Digital part:

- 4 analog watchdogs comparing ADC results against predefined levels (low, high, range) before results are stored in the appropriate ADC result location

- 2 modes of operation: CPU Mode or CTU Mode

- CPU mode features

- Register based interface with the CPU: one result register per channel

- ADC state machine managing three request flows: regular command, hardware injected command, software injected command

- Selectable priority between software and hardware injected commands

- 4 analog watchdogs comparing ADC results against predefined levels (low, high, range)

- DMA compatible interface

- CTU mode features

- Triggered mode only

- 4 independent result queues (1  $\times$  16 entries, 2  $\times$  8 entries, 1  $\times$  4 entries)

- Result alignment circuitry (left justified; right justified)

- 32-bit read mode allows to have channel ID on one of the 16-bit parts

- DMA compatible interfaces

- Built-in self-test features triggered by software

#### 1.5.34 Cross triggering unit (CTU)

The ADC cross triggering unit allows automatic generation of ADC conversion requests on user selected conditions without CPU load during the PWM period and with minimized CPU load for dynamic configuration.

The CTU implements the following features:

- Cross triggering between ADC, FlexPWM, eTimer, and external pins

- Double buffered trigger generation unit with as many as 8 independent triggers generated from external triggers

- Maximum operating frequency less than or equal to 120 MHz

- Trigger generation unit configurable in sequential mode or in triggered mode

- Trigger delay unit to compensate the delay of external low pass filter

- Double buffered global trigger unit allowing eTimer synchronization and/or ADC command generation

- Double buffered ADC command list pointers to minimize ADC-trigger unit update

- Double buffered ADC conversion command list with as many as 24 ADC commands

- Each trigger capable of generating consecutive commands

- ADC conversion command allows control of ADC channel from each ADC, single or synchronous sampling, independent result queue selection

- DMA support with safety features

#### 1.5.35 Cyclic redundancy checker (CRC) unit

The CRC module is a configurable multiple data flow unit to compute CRC signatures on data written to its input register.

The CRC unit has the following features:

- 3 sets of registers to allow 3 concurrent contexts with possibly different CRC computations, each with a selectable polynomial and seed

- Computes 16- or 32-bit wide CRC on the fly (single-cycle computation) and stores result in internal register.

The following standard CRC polynomials are implemented:

- $x^8 + x^4 + x^3 + x^2 + 1$  [8-bit CRC]

- $-x^{16} + x^{12} + x^5 + 1$  [16-bit CRC-CCITT]

- $x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$ [32-bit CRC-ethernet(32)]

- Key engine to be coupled with communication periphery where CRC application is added to allow implementation of safe communication protocol

- Offloads core from cycle-consuming CRC and helps checking configuration signature for safe start-up or periodic procedures

- CRC unit connected as peripheral bus on internal peripheral bus

- DMA support

#### 1.5.36 Redundancy control and checker unit (RCCU)

The RCCU checks all outputs of the sphere of replication (addresses, data, control signals). It has the following features:

- Duplicated module to guarantee highest possible diagnostic coverage (check of checker)

- Multiple times replicated IPs are used as checkers on the SoR outputs

#### 1.5.37 Junction temperature sensor

The junction temperature sensor provides a value via an ADC channel that can be used by software to calculate the device junction temperature.

The key parameters of the junction temperature sensor include:

- Nominal temperature range from –40 to 150 °C

- Software temperature alarm via analog ADC comparator possible

#### 1.5.38 Nexus port controller (NPC)

The NPC module provides real-time development support capabilities for this device in compliance with the IEEE-ISTO 5001-2008 standard. This development support is supplied for MCUs without requiring external address and data pins for internal visibility.

The NPC block interfaces to the host processor and internal buses to provide development support as per the IEEE-ISTO 5001-2008 Class 3+, including selected features from Class 4 standard.

The development support provided includes program trace, data trace, watchpoint trace, ownership trace, run-time access to the MCUs internal memory map and access to the Power Architecture internal registers during halt. The Nexus interface also supports a JTAG only mode using only the JTAG pins. The following features are implemented:

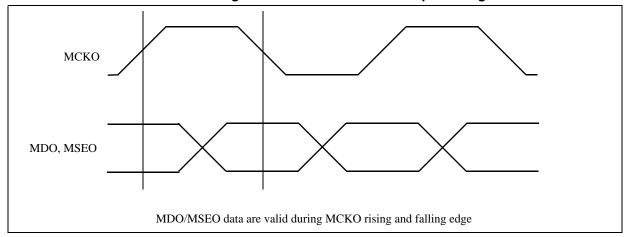

- Full and reduced port modes

- MCKO (message clock out) pin

- 4 or 12 MDO (message data out) pins<sup>(b)</sup>

- 2 MSEO (message start/end out) pins

- EVTO (event out) pin

- Auxiliary input port

- EVTI (event in) pin

- 5-pin JTAG port (JCOMP, TDI, TDO, TMS, and TCK)

- Supports JTAG mode

- Host processor (e200) development support features

- Data trace via data write messaging (DWM) and data read messaging (DRM).

This allows the development tool to trace reads or writes, or both, to selected internal memory resources.

- Ownership trace via ownership trace messaging (OTM). OTM facilitates

ownership trace by providing visibility of which process ID or operating system

task is activated. An ownership trace message is transmitted when a new

process/task is activated, allowing development tools to trace ownership flow.

- Program trace via branch trace messaging (BTM). Branch trace messaging displays program flow discontinuities (direct branches, indirect branches, exceptions, etc.), allowing the development tool to interpolate what transpires between the discontinuities. Thus, static code may be traced.

- Watchpoint messaging (WPM) via the auxiliary port

b. 4 MDO pins on LQFP144 package

- Watchpoint trigger enable of program and/or data trace messaging

- Data tracing of instruction fetches via private opcodes

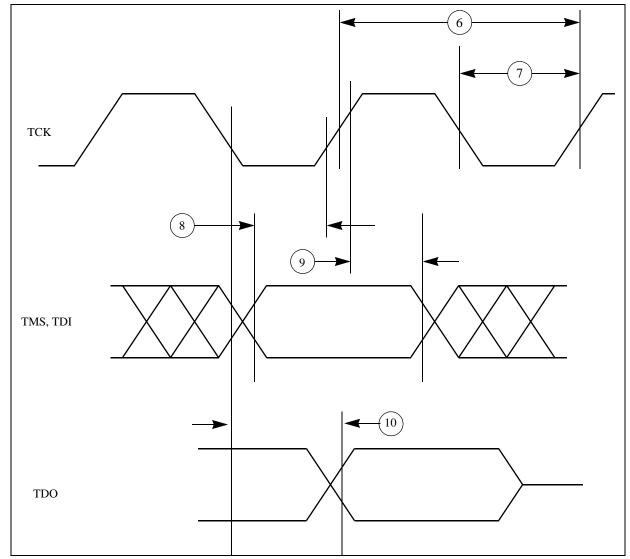

#### 1.5.39 IEEE 1149.1 JTAG controller (JTAGC)

The JTAGC block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. All data input to and output from the JTAGC block is communicated in serial format. The JTAGC block is compliant with the IEEE standard.

The JTAG controller provides the following features:

- IEEE Test Access Port (TAP) interface with 5 pins:

- TDI

- TMS

- TCK

- TDO

- JCOMP

- Selectable modes of operation include JTAGC/debug or normal system operation

- 5-bit instruction register that supports the following IEEE 1149.1-2001 defined instructions:

- BYPASS

- IDCODE

- EXTEST

- SAMPLE

- SAMPLE/PRELOAD

- 3 test data registers: a bypass register, a boundary scan register, and a device identification register. The size of the boundary scan register is parameterized to support a variety of boundary scan chain lengths.

- TAP controller state machine that controls the operation of the data registers, instruction register and associated circuitry

#### 1.5.40 Voltage regulator / power management unit (PMU)

The on-chip voltage regulator module provides the following features:

- Single external rail required

- Single high supply required: nominal 3.3 V both for packaged and Known Good Die option

- Packaged option requires external ballast transistor due to reduced dissipation capacity at high temperature but can use embedded transistor if power dissipation is maintained within package dissipation capacity (lower frequency of operation)

- Known Good Die option uses embedded ballast transistor as dissipation capacity is increased to reduce system cost

- All I/Os are at same voltage as external supply (3.3 V nominal)

- Duplicated Low-Voltage Detectors (LVD) to guarantee proper operation at all stages (reset, configuration, normal operation) and, to maximize safety coverage, one LVD can be tested while the other operates (on-line self-testing feature)

DocID023953 Rev 5

31/128

#### 1.5.41 Built-In self-test (BIST) capability

This device includes the following protection against latent faults:

- Boot-time Memory Built-In Self-Test (MBIST)