# 2911A-1 **PCM CODEC—A LAW** 8-BIT COMPANDED A/D AND D/A CONVERTER

- Per Channel, Single Chip Codec

- **CCITT G711 and G732 Compatible**, **Even Order Bits Inversion Included**

- Microcomputer Interface with On-Chip **Time-Slot Computation**

- Simple Direct Mode Interface When **Fixed Timeslots Are Used**

- $\pm$ 5% Power Supplies: + 12V. +5V. -5V

- 66 dB Dynamic Range, with Resolution **Equivalent to 11-Bit Linear Conversion Around Zero**

- Precision On-Chip Voltage Reference

- **Low Power Consumption 230 mW Typ.** Standby Power 33 mW Typ.

- Fabricated with Reliable N-Channel **MOS Process**

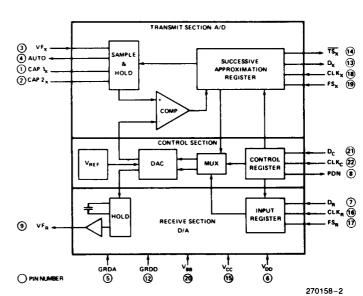

The Intel 2911A is a fully integrated PCM (Pulse Code Modulation) Codec (Coder-Decoder), fabricated with N-channel silicon gate technology. The high density of integration allows the sample and hold circuits, the digital-to-analog converter, the comparator and the successive approximation register to be integrated on the same chip, along with the logic necessary to interface a full duplex PCM link.

The primary applications are in telephone systems:

- Transmission

- 30/32 Channel Systems at 2.048 Mbps

- Switching

- Digital PBX's and Central Office Switching Systems

- Concentration Subscriber Carrier/Concentrators

The wide dynamic range of the 2911A (66 dB) and the minimal conversion time (80 µs minimum) make it an ideal product for other applications, like:

Data Acquisition

Secure Communications Systems

Telemetry

Signal Processing Systems

Figure 1. Pin Configuration

| CARA CARA                                              | Lielding Consoitor |

|--------------------------------------------------------|--------------------|

| CAP 1 <sub>X</sub> , CAP 2 <sub>X</sub>                | Holding Capacitor  |

| VF <sub>X</sub>                                        | Analog Input       |

| VFR                                                    | Analog Output      |

| D <sub>R</sub> , D <sub>C</sub>                        | Digital Input      |

| D <sub>X</sub> , TS <sub>X</sub>                       | Digital Output     |

| CLK <sub>C</sub> , CLK <sub>X</sub> , CLK <sub>R</sub> | Clock Input        |

| FS <sub>X</sub> , FS <sub>R</sub>                      | Frame Sync Input   |

| AUTO                                                   | Auto Zero Output   |

| V <sub>BB</sub>                                        | Power (-5V)        |

| Vcc                                                    | Power (+ 5V)       |

| V <sub>DD</sub>                                        | Power (+ 12V)      |

| PON                                                    | Power Down         |

| GRDA                                                   | Analog Ground      |

| GRDD                                                   | Digital Ground     |

| NC                                                     | No Connect         |

Figure 2. Pin Names

Figure 3. Block Diagram

November 1986 Order Number: 270158-001

# PIN DESCRIPTION

| Pin No | Symbol            | Function | Description                                                                                                                                                                                                                                                                                       |

|--------|-------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | CAP1 <sub>X</sub> | Hold     | Connections for the transmit holding capacitor. Refer to                                                                                                                                                                                                                                          |

| 2      | CAP2 <sub>X</sub> | 7        | Applications section.                                                                                                                                                                                                                                                                             |

| 3      | VF <sub>X</sub>   | Input    | Analog input to be encoded into a PCM word. The signal on this lead is sampled at the same rate as the transmit frame synchronization pulse $FS_X$ , and the sample value is held in the external capacitor connected to the $CAP1_X$ and $CAP2_X$ leads until the encoding process is completed. |

| 4      | AUTO              | Output   | Most significant bit of the encoded PCM word (+5V for negative, -5V for positive values). Refer to the Codec Applications section.                                                                                                                                                                |

| 5      | GRDA              | Ground   | Analog return common to the transmit and receive analog circuits. Not connected to GRDD internally.                                                                                                                                                                                               |

| 6      | V <sub>DD</sub>   | Power    | + 12V ±5%; referenced to GRDA.                                                                                                                                                                                                                                                                    |

| 7      | D <sub>R</sub>    | Input    | Receive PCM highway (serial bus) interface. The Codec serially receives a PCM word (8 bits) through this lead at the proper time defined by FS <sub>R</sub> , CLK <sub>R</sub> , D <sub>C</sub> , and CLK <sub>C</sub> .                                                                          |

| 8      | PDN               | Output   | Active high when the Codec is in the power down state. Open drain output.                                                                                                                                                                                                                         |

| 9      | VFR               | Output   | Analog Output. The voltage present on VF <sub>R</sub> is the decoded value of the PCM word received on lead D <sub>R</sub> . This value is held constant between two conversions.                                                                                                                 |

| 10     | NC                | No       | Recommended practice is to strap these NC's to GRDA.                                                                                                                                                                                                                                              |

| 11     | NC                | Connects |                                                                                                                                                                                                                                                                                                   |

| 12     | GRDD              | Ground   | Ground return common to the logic power supply; V <sub>CC</sub> .                                                                                                                                                                                                                                 |

| 13     | D <sub>X</sub>    | Output   | Output of the transmit side onto the send PCM highway (serial bus). The 8-bit PCM word is serially sent out on this pin at the proper time defined by FS <sub>X</sub> , CLK <sub>X</sub> , D <sub>C</sub> , and CLK <sub>C</sub> . TTL three-state output.                                        |

| 14     | TS <sub>X</sub>   | Output   | Normally high, this signal goes low while the Codec is transmitting an 8-bit PCM word on the $D_X$ lead. (Timeslot information used for diagnostic purposes and also to gate the data on the $D_X$ lead.) Open drain output.                                                                      |

| 15     | V <sub>CC</sub>   | Power    | +5V ±5%, referenced to GRDD.                                                                                                                                                                                                                                                                      |

| 16     | CLK <sub>R</sub>  | Input    | Master receive clock defining the bit rate on the receive PCM highway. Typically 2.048 Mbps for a carrier system. Maximum rate 2.1 Mbps. 50% duty cycle. TTL compatible.                                                                                                                          |

| 17     | FS <sub>R</sub>   | Input    | Frame synchronization pulse for the receive PCM highway. Resets the on-chip timeslot counter for the receive side. Maximum repetition rate 12 KHz. TTL interface.                                                                                                                                 |

| 18     | CLKX              | Input    | Master transmit clock defining the bit rate on the transmit PCM highway. Typically 2.048 Mbps for a carrier system. Maximum rate 2.1 Mbps. 50% duty cycle. TTL interface.                                                                                                                         |

| 19     | FS <sub>X</sub>   | Input    | Frame synchronization pulse for the transmit PCM highway. Resets the on-chip timeslot counter for the transmit side. Maximum repetition rate 12 KHz. TTL interface.                                                                                                                               |

| 20     | $V_{BB}$          | Power    | -5V ±5%, referenced to GRDA.                                                                                                                                                                                                                                                                      |

| 21     | D <sub>C</sub>    | Input    | Data input to program the Codec for the chosen mode of operation. Becomes an active low chip select when CLK <sub>C</sub> is tied to V <sub>CC</sub> . TTL interface.                                                                                                                             |

| 22     | CLK <sub>C</sub>  | Input    | Clock input to clock in the data on the D <sub>C</sub> lead when the timeslot assignment feature is used; tied to V <sub>CC</sub> to disable this feature. TTL interface.                                                                                                                         |

#### **FUNCTIONAL DESCRIPTION**

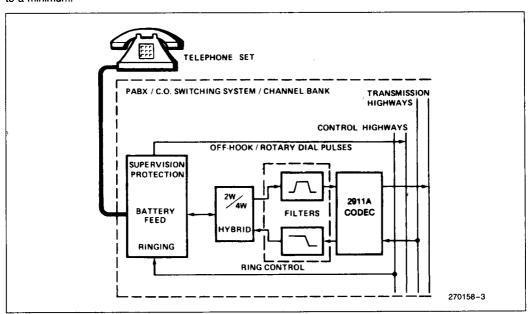

The 2911A PCM Codec provides the analog-to-digital and the digital-to-analog conversions necessary to interface a full duplex (4 wires) voice telephone circuit with the PCM highways of a time division multiplexed (TDM) system. The Codec is intended to be used on line and trunk terminations.

In a typical telephone system the Codec is located between the PCM highways and the channel filters.

The Codec encodes the incoming analog signal at the frame rate (FS<sub>X</sub>) into an 8-bit PCM word which is sent out on the D<sub>X</sub> lead at the proper time. Similarly, on the receive link, the Codec fetches an 8-bit PCM word from the receive highway (D<sub>R</sub> lead) and decodes an analog value which will remain constant on lead VF<sub>R</sub> until the next receive frame. Transmit and receive frames are independent. They can be asynchronous (transmission) or synchronous (switching) with each other.

Circuitry is provided within the Codec to internally define the transmit and receive timeslots. In small systems this may eliminate the need for any external timeslot exchange; in large systems it provides one level of concentration. This feature can be bypassed and discrete timeslots sent to each Codec within a system.

In the power-down mode, most functions of the Codec are directly disabled to reduce power dissipation to a minimum.

#### **CODEC OPERATION**

#### **Codec Control**

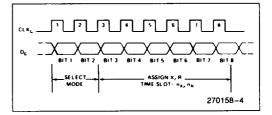

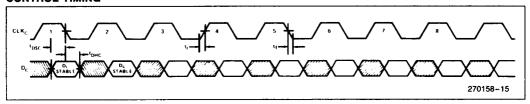

The operation of the 2911A is defined by serially loading an 8-bit word through the  $D_C$  lead (data) and the CLK $_C$  lead (clock). The loading is synchronous with the other operations of the Codec, and takes place whenever transitions occur on the CLK $_C$  lead. The  $D_C$  input is loaded in during the trailing edge of the CLK $_C$  input.

The control word contains two fields:

Bit 1 and Bit 2 define whether the subsequent 6 bits apply to both the transmit and receive side (00), the transmit side only (01), the receive side only (10), or whether the Codec should go into the standby, power-down mode (11). In the last case (11), the following 6 bits are irrelevant.

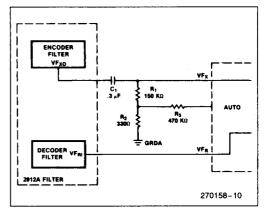

Figure 4. Typical Line Termination

5

The last 6 bits of the control word define the timeslot assignment, from 000000 (timeslot 1) to 1111111 (timeslot 64). Bit 3 is the most significant bit and bit 8 the least significant bit and last into the Codec.

| Bit 1 | Bit 2 | Mode    |

|-------|-------|---------|

| 0     | 0     | X&R     |

| 0     | 1     | Х       |

| 1     | 0     | R       |

| 1     | 1     | Standby |

|   |   | В | Time Clet |   |   |           |

|---|---|---|-----------|---|---|-----------|

| 3 | 4 | 5 | 6         | 7 | 8 | Time-Slot |

| 0 | 0 | 0 | 0         | 0 | 0 | 1         |

| 0 | 0 | 0 | 0         | 0 | 1 | 2         |

|   |   |   | •         |   |   | •         |

|   |   | • | •         |   |   | •         |

|   |   | ( | •         |   |   | •         |

|   |   | • | •         |   |   | •         |

| 1 | 1 | 1 | 1         | 1 | 1 | 64        |

The Codec will retain the control word (or words) until a new word is loaded in or until power is lost. This feature permits dynamic allocation of timeslots for switching applications.

# **Microcomputer Control Mode**

In the microcomputer mode, each Codec performs its own timeslot computation independently for the transmit and receive channels by counting clock pulses (CLKy and CLKR). All Codecs tied to the same data bus receive identical framing pulses (FSX and FS<sub>R</sub>). The framing pulses reset the on-chip timeslot counters every frame; hence the timeslot counters of all devices are synchronized. Each Codec is programmed via CLKC and DC for the desired transmit and receive timeslots according to the description in the Codec Control Section. All Codecs tied to the same DR bus will, in general, have different receive timeslots, although that is not a device requirement. There may be separate busses for transmit and receive or all Codecs may transmit and receive over the same bus, in which case the transmit and receive channels must be synchronous (CLK<sub>X</sub> = CLK<sub>B</sub>). There are no other restrictions on timeslot assignments; a device may have the same transmit and receive timeslot even if a single bus is used.

There are several requirements for using the  $CLK_C-D_C$  interface in the microcomputer mode.

A complete timeslot assignment, consisting of eight negative transitions of CLK<sub>C</sub>, must be made in less than one frame period. The assignment

- can overlap a framing pulse so long as all 8 control bits are clocked in within a total span of 125  $\mu s$  (for an 8 KHz frame rate). CLK $_{C}$  must be left at a TTL low level when not assigning a time-slot.

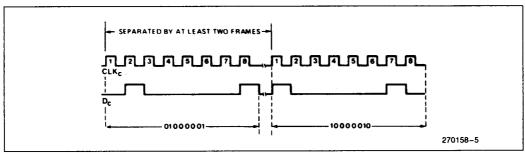

- A dead period of two frames must always be observed between successive timeslot assignments. The two frame delay is measured from the rising edge of the first CLK<sub>C</sub> transition of the previous timeslot assigned.

- When the device is in the power-down state (Standby), the following three-step sequence must be followed to power-up the codec to avoid contention on the transmit PCM highway.

- a. Assign a dummy transmit timeslot. The dummy should be at least two timeslots greater than the maximum valid system (usually 24 or 32). For example, in a 24 timeslot system, the dummy could be any timeslot between 26 and 64. This will power-up the transmit side, but prevent any spurious Dx or TSx outputs.

- two frames later, assign the desired transmit timeslot.

- c. Two frames later assign the desired receive timeslot.

- 4. Initialization sequence: The device contains an on-chip power-on clear function which guarantees that with proper sequencing of the supplies (V<sub>CC</sub> or V<sub>DD</sub> on last), the device will initialize with no timeslot assigned to either the transmit or receive channel. After a supply failure or whenever the supplies are applied, it is recommended that either power down assignment be made first, or the first timeslot assignment be a transmit timeslot or a transmit/receive timeslot. The consequence of making a receive timeslot assignment first, after supply application, is that the transmit channel will assume timeslot 1, potentially producing bus contention.

- 5. Transmit only/receive only operation is permitted provided that a power down assignment is made first. Otherwise, special circuits which use only one channel should be physically disconnected from the unused bus; this allows a timeslot to be made to an unused channel without consequence.

- Both frame synchronizing pulses (FS<sub>X</sub>, FS<sub>R</sub>) must be active at all times after power on clear (after power supplies are turned on). This requirement must be met during powerdown and receive only or transmit only operation, as well as during normal transmit and receive operation.

Example of Microcomputer Control Mode:

The two words 01000001 and 10000010 have been loaded into the Codec. The transmit side is now programmed for timeslot 2 and the receive side for

timeslot 3. The Codec will output a PCM word on the transmit PCM highway (bus) during the timeslot 2 of the transmit frame, and will fetch a PCM word from the receive PCM highway during timeslot 3.

Figure 5. Microcomputer Mode Programming Examples

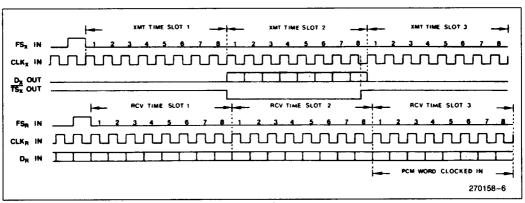

In this example the Codec interface to the PCM highway then functions as shown below. (FS<sub>X</sub> and FS<sub>R</sub> may be asynchronous.)

Figure 6. Microcomputer Mode PCM Highway Example

#### **Direct Control Mode**

The direct mode of operation will be selected when the  $CLK_C$  pin is strapped to the +5V supply  $(V_{CC})$ . In this mode, the  $D_C$  pin is an active low chip select. In other words, when  $D_C$  is low, the device transmits and receives in the timeslots which follow the appropriate framing pulses. With  $D_C$  high the device is in the power down state. Even though  $CLK_C$  characteristics are simpler for the 2911A it will operate properly when plugged into a 2911 board.

Deactivation of a channel by removal of the appropriate framing pulse (FS<sub>X</sub> or FS<sub>B</sub>) is not permitted.

Specifically, framing pulses must be applied for a minimum of two frames after a change in state of  $D_C$  in order for the  $D_C$  change to be internally sensed. In particular, when entering standby in the direct mode, framing pulses must be applied as usual for two frames after  $D_C$  is brought high.

The Codec will enter direct mode within three frame times (375  $\mu$ s) as measured from the time the device power supplies settle to within the specified limits. This assumes that CLK<sub>C</sub> is tied to V<sub>CC</sub> and that all clocks are available at the time the supplies have settled.

# General Control Requirements

All bit and frame clocks should be applied whenever the device is active. In particular, an unused channel cannot be deactivated by removal of its associated frame or bit clock while the other channel of the same device remains active.

A single channel cannot be deactivated except by physical disconnection of the data lead ( $D_X$  or  $D_R$ ) from the system data bus. A device (both transmit and receive channels) may be deactivated in either control mode by powering down the device. Both channels are always powered down together.

## **Encoding**

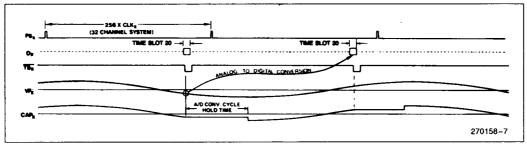

The VF signal to be encoded is input on the VF $_{\rm X}$  lead. An internal switch samples the signal and the hold function is performed by the external capacitor connected to the CAP1 $_{\rm X}$  and CAP2 $_{\rm X}$  leads. The

sampling and conversion is synchronized with the transmit timeslot. The PCM word is then output on the  $D_X$  lead at the proper timeslot occurrence of the following frame. The A/D converter saturates at approximately  $\pm 2.2 V$  RMS ( $\pm 3.1 V$  peak).

Figure 7. Transmit Encoding

## **Decoding**

The PCM word is fetched by the  $D_R$  lead from the PCM highway at the proper timeslot occurrence. The decoded value is held on an internal sample and hold capacitor. The buffered non-return to zero output signal on the VF $_R$  lead has a dynamic range of  $\pm 2.2$ V RMS ( $\pm 3.1$  volts peak).

# Standby Mode—Power Down

To minimize power consumption and heat dissipation a standby mode is provided where all Codec functions are disabled except for  $D_{C}$  and  $CLK_{C}$  leads. These allow the Codec to be reactivated. In the microcomputer mode the Codec is placed into standby by loading a control word ( $D_{C}$ ) with a "1" in bits 1 and 2 locations. In the direct mode when  $D_{C}$  is brought high, the all "1's" control word is internally transferred to the control register, invoking the standby condition.

While in the standby mode, the  $D_X$  output is actively held in a high impedance state to guarantee that the PCM bus will not be driven.

The power consumption in the standby mode is typically 33 mW.

#### Power-On Clear

Whether the device is used in the direct or microcomputer mode, an internal reset (power-on clear) is generated, forcing the device into the power down state, when power is supplied by any of the following methods. (1) Device power supplies are turned on in a system power-up situation where either  $V_{CC}$  or  $V_{DD}$  is applied last. (2) A large supply transient causes either of the two positive supplies to drop to approximately 2V. (3) A board containing Codecs is plugged into a "hot" system where  $V_{CC}$  or  $V_{DD}$  is the last contact made. It may be necessary to trim back the edge connector pins or fingers on  $V_{CC}$  or  $V_{DD}$  relative to the other supply to guarantee that the power-on clear will operate properly when a board is plugged into a "hot" system. Furthermore, the Codec will inhibit activity on  $\overline{\mbox{TS}}_{\chi}$  and  $\mbox{D}_{\chi}$  during the application of power supplies.

The device is also tolerant of transients in the negative supply ( $V_{BB}$ ) so long as  $V_{BB}$  remains more negative than -3.5V.  $V_{BB}$  transients which exceed this level should be detected and followed by a system reinitialization.

# Precision Voltage Reference for the D/A Converter

The voltage reference is generated on the chip and is calibrated during the manufacturing process. The technique uses the difference in sub-surface charge density between two suitably implanted MOS devices to derive a temperature stable and bias stable reference voltage.

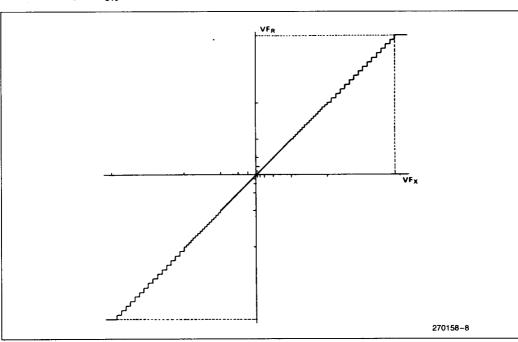

#### **CONVERSION LAW**

The conversion law is commonly referred to as the A Law.

$$F(x) = Sgn(x) \left[ \frac{1 + log_{10} (A|X|)}{1 + log_{10} A} \right], \quad 1/A \le |x| \le 1$$

$$F(x) = Sgn(x) \left[ \frac{A|X|}{1 + log_{10} A} \right], \quad 0 \le |x| \le 1/A$$

where: x = the input signal

Sgn(x) = sign of the input signal

A = 87.6 (defined by CCITT)

The Codec provides a piecewise linear approximation of the logarithmic law through 13 segments. Each segment is made of 16 steps with the exception of the first segment, which has 32 steps. In adjacent segments the step sizes are in a ratio of two to one. Within each segment, the step size is constant.

The output levels are midway between the corresponding decision levels. The output levels  $y_n$  are related to the input levels  $x_n$  by the expression:

$$y_n = \frac{x_{n-1} + x_n}{2}, \quad 0 < n \le 128$$

Figure 10. Codec Transfer Characteristic

#### Theoretical A-Law—Positive Input Values (for Negative Input Values, Invert Bit 1)

| 1       | 2                                     | 3                   | 4                 | 5                        | 6                             | 7                                                  | 8                 |

|---------|---------------------------------------|---------------------|-------------------|--------------------------|-------------------------------|----------------------------------------------------|-------------------|

| Segment | No. of Steps                          | Value at<br>Segment | Decision<br>Value | Decision                 | PCM Word <sup>(4)</sup>       | Normalized<br>Value                                | Decoder<br>Output |

| Number  | x Step Size                           | End Points          | Number n          | Value x <sub>n</sub> (1) | Bit Number<br>1 2 3 4 5 6 7 8 | at Decoder<br>Output y <sub>n</sub> <sup>(5)</sup> | Value<br>Number   |

|         |                                       | 4096(3)             | (128)             | (4096)                   |                               | 1<br>4032                                          | 1 1               |

|         |                                       |                     | 127               | 3968                     | 1111111                       | 4032<br>                                           | 128               |

| _       |                                       | 1                   | 1                 |                          |                               | !                                                  |                   |

| 7       | 16 x 128                              |                     | į                 | į į                      | (Note 2)                      | i                                                  | ļi                |

|         |                                       |                     | 113               | 2176                     |                               | . I                                                |                   |

|         |                                       | 2048                | 112               | 2048                     | 11110000                      | 2112                                               | 113               |

|         |                                       | 2046                | 112               | 2048                     |                               | i                                                  | i                 |

| 6       | 16 x 64                               | a                   | !                 | 1                        | (Note 2)                      | 1                                                  | !                 |

|         |                                       |                     | <u>i</u>          | i .                      |                               | i                                                  | i                 |

|         |                                       |                     | 97                | 1088                     | 11100000                      | 1056                                               | 97                |

|         |                                       | 1024                | 96<br>I           | 1024                     |                               | !                                                  | 1                 |

| 5       | 16 x 32                               |                     | i :               |                          | (Note 2)                      | 1                                                  | ;                 |

| -       |                                       |                     |                   |                          | (10.0 2)                      | <br>                                               | 1                 |

|         | · · · · · · · · · · · · · · · · · · · | ļ                   | 81                | 544                      |                               | i                                                  | i                 |

|         |                                       | 512                 | 80                | 512                      | 11010000                      | 528<br>I                                           | 81<br>I           |

|         |                                       |                     |                   |                          |                               | 1                                                  |                   |

| 4       | 16 x 16                               |                     | i                 | į                        | (Note 2)                      | i                                                  | i                 |

|         |                                       |                     | l<br>65           | 272                      |                               | I<br>I                                             |                   |

|         |                                       | 256                 | 64                | 256                      | 11000000                      | 264                                                | 65                |

|         |                                       | 256                 | 1<br>             | 256                      |                               | i                                                  | ;                 |

| 3       | 16 x 8                                |                     |                   |                          | (Note 2)                      | ]<br>                                              |                   |

|         |                                       |                     | I                 | i                        |                               | į                                                  | į į               |

|         |                                       | 1                   | 49                | 136                      | 10110000                      | 1<br>132                                           | 49                |

|         |                                       | 128                 | 48                | 128                      |                               | 1                                                  | I I               |

| 2       | 16 x 4                                |                     | į                 | l į                      | (Note 2)                      | į                                                  | i                 |

|         |                                       |                     |                   |                          |                               | <br>                                               |                   |

|         |                                       | -                   | 33                | 68                       | 10100000                      | l<br>66                                            | 1                 |

|         |                                       | 64                  | 32                | 64                       | 1010000                       | l<br>I                                             | 33<br>I           |

|         | 20 11 0                               |                     |                   |                          | (1)                           | Į<br>I                                             |                   |

| 1       | 32 x 2                                |                     |                   | i                        | (Note 2)                      | į                                                  |                   |

|         |                                       | ]                   | 1                 | 2                        |                               | i<br>i                                             |                   |

|         |                                       | ]                   |                   | l                        | 10000000                      | 1                                                  | 1 1               |

#### NOTES

- 1. 4096 normalized value units correspond to the value of the on-chip voltage reference.

- 2. The PCM word corresponding to positive input values between two successive decision values numbered n and n+1 (see column 4) is (128 + n) expressed as a binary number.

- 3. X<sub>128</sub> is a virtual decision value.

- 4. The PCM word on the highways is the same as the one shown in column 6, with the even order bits inverted. The 2911A provides for the inversion of the even order bits on both the send and receive sections.

- $^{5}$ . The voltage output on the VF<sub>R</sub> lead is equal to the normalized value given in the table, augmented by an offset. The offset value is approximately 15 mV.

#### APPLICATIONS

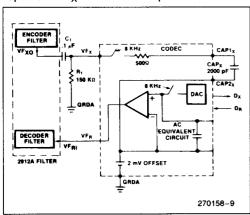

## **Holding Capacitor**

For an 8 KHz sampling system the transmit holding capacitor  $CAP_X$  should be 2000 pF  $\pm 20\%$ .

Figure 11. Circuit Interface—Without External Auto Zero

#### Filters Interface

The filters may be interfaced as shown in the circuit interface diagrams. Note that the output pulse stream is of the non-return-to-zero type and hence requires the (sin x)/x correction provided by the 2912A filter.

#### D<sub>Y</sub> Buffering

For higher drive capability or increased system reliability it may be desirable that the  $D_X$  output of a group of Codecs be buffered from the system PCM bus with an external three-state or open collector buffers. A buffer can be enabled with the appropriate Codec generated  $\overline{TS}_X$  signal or signals.  $\overline{TS}_X$  signal may also be used to activate external zero code suppression logic, since the occurrence of an active state of any  $\overline{TS}_X$  implies the existence of PCM voice bits (as opposed to transparent data bits) on the bus.

Figure 12. Circuit Interface—With External Auto Zero

#### **Auto Zero**

The 2911A contains a transparent on-chip auto zero plus a device pin for implementing a sign-bit driven external auto zero feedback loop. The on-chip auto zero reduces the input offset voltage of the encoder (VF $_X$ ) to less than 3 mV. For most telephony applications, this input offset is perfectly acceptable, since it insures the encoder is biased in the lower 25% of the first segment.

Where lower input offset is required the external auto zero loop may be used to bias the encoder exactly at the zero crossing point. The consequence of the external auto zero loop, aside from extra components, is the addition of the dithering auto-zero signal to the input signal, resulting in slightly higher idle channel noise (approximately 2 dB) than when the external loop is not used. Consequently, where the application permits, it is recommended that the external auto zero loop not be used. When not used, the AUTO pin should float.

The circuit interface with external auto zero drawing shows a possible connection between VF $_{\rm X}$  and AUTO leads with the recommended values of C $_1$ =0.3  $\mu$ F, R $_1$ =150 K $\Omega$ , R $_2$ =330 $\Omega$ , and R $_3$ =470 K $\Omega$ .

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias 10°C to +80°C                                      |

|---------------------------------------------------------------------------|

| Storage Temperature $\dots -65^{\circ}\text{C}$ to $+150^{\circ}\text{C}$ |

| All Input or Output Voltages with                                         |

| Respect to V <sub>BB</sub> 0.3V to +20V                                   |

| V <sub>CC</sub> , V <sub>DD</sub> , GRDA, and GRDA with Respect           |

| to V <sub>BB</sub> 0.3V to +20V                                           |

| Power Dissipation1.35W                                                    |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

#### D.C. CHARACTERISTICS

$T_A=0^{\circ}C$  to  $+70^{\circ}C$  ,  $V_{DD}=+12V~\pm5\%$  ,  $V_{CC}=+5V~\pm5\%$  ,  $V_{BB}=-5V~\pm5\%$  , GRDA = 0V, GRDD = 0V, unless otherwise specified.

#### **DIGITAL INTERFACE**

| Symbol          | Parameter                | Limits |                    |     | Unit | Test Conditions                                                                                                          |  |

|-----------------|--------------------------|--------|--------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------|--|

|                 | rarameter                | Min    | Typ <sup>(1)</sup> | Max | Unit | rest conditions                                                                                                          |  |

| I <sub>IL</sub> | Low Level Input Current  |        |                    | 10  | μΑ   | $V_{IN} < V_{IL}$                                                                                                        |  |

| l <sub>iH</sub> | High Level Input Current |        |                    | 10  | μΑ   | $V_{IN} > V_{IH}$                                                                                                        |  |

| V <sub>IL</sub> | input Low Voltage        |        |                    | 0.6 | ٧    |                                                                                                                          |  |

| V <sub>IH</sub> | Input High Voltage       | 2.2    |                    |     | ٧    |                                                                                                                          |  |

| V <sub>OL</sub> | Output Low Voltage       |        |                    | 0.4 | ٧    | $D_{X}$ , $I_{OL} = 4.0$ mA<br>$\overline{TS_{X}}$ , $I_{OL} = 3.2$ mA, open drain<br>PDN, $I_{OL} = 1.6$ mA, open drain |  |

| V <sub>OH</sub> | Output High Voltage      | 2.4    |                    |     | ٧    | D <sub>X</sub> , I <sub>OH</sub> = 15 mA                                                                                 |  |

#### **ANALOG INTERFACE**

| Symbol          | Parameter                                         |                      | Limits          |                       | Unit | Test Conditions                                                            |  |

|-----------------|---------------------------------------------------|----------------------|-----------------|-----------------------|------|----------------------------------------------------------------------------|--|

| Cymbol          | r arameter                                        | Min                  | Typ(1)          | Max                   |      | rest conditions                                                            |  |

| Z <sub>AI</sub> | Input Impedance when<br>Sampling, VF <sub>X</sub> | 125                  | 300             | 500                   | Ω    | In series with CAP <sub>X</sub> to GRDA,<br>-3.1V < V <sub>IN</sub> < 3.1V |  |

| Z <sub>AO</sub> | Small Signal Output<br>Impedance, VF <sub>R</sub> | 100                  | 180             | 300                   | Ω    | -3.1V < V <sub>OUT</sub> < 3.1V                                            |  |

| V <sub>OR</sub> | Output Offset Voltage at VFR                      | -50                  |                 | 50                    | m۷   | Minimum code to DR                                                         |  |

| V <sub>IX</sub> | Input Offset Voltage at VFX                       | -5                   |                 | 5                     | mV   | Minimum positive code produced at D <sub>X</sub>                           |  |

| V <sub>OL</sub> | Output Low Voltage at AUTO                        |                      | V <sub>BB</sub> | (V <sub>BB</sub> + 2) | ٧    | 400 KΩ to GRDA                                                             |  |

| V <sub>OH</sub> | Output High Voltage at AUTO                       | (V <sub>CC</sub> -2) | V <sub>CC</sub> |                       | ٧    | 400 KΩ to GRDA                                                             |  |

#### D.C. CHARACTERISTICS

$T_A = 0$ °C to +70°C,  $V_{DD} = +12$ V  $\pm 5$ %,  $V_{CC} = +5$ V  $\pm 5$ %,  $V_{BB} = -5$ V  $\pm 5$ %, GRDA = 0V, GRDD = 0V, unless otherwise specified. (Continued)

#### **POWER DISSIPATION**

| Symbol           | Parameter         |     | Limits Unit Test Condi |     | Limits |                             | ts   Unit   Test Cond |  |  |

|------------------|-------------------|-----|------------------------|-----|--------|-----------------------------|-----------------------|--|--|

| Зупівої          | raiametei         | Min | Typ(1)                 | Max | Jt     | Tost Gondinone              |                       |  |  |

| IDDO             | Standby Current   |     | 0.7                    | 1.1 | mA     |                             |                       |  |  |

| Icco             | Standby Current   |     | 4.0                    | 7.0 | mA     |                             |                       |  |  |

| I <sub>BBO</sub> | Standby Current   |     | 1.0                    | 2.5 | mA     | Auto Output = Open          |                       |  |  |

| I <sub>DDI</sub> | Operating Current |     | 11                     | 16  | mA     | Clock Frequency = 2.048 MHZ |                       |  |  |

| lcci             | Operating Current |     | 13                     | 21  | mA     |                             |                       |  |  |

| I <sub>BBI</sub> | Operating Current |     | 4.0                    | 6.0 | mA     |                             |                       |  |  |

#### NOTE:

#### A.C. CHARACTERISTICS

$T_A$  = 0°C to +70°C,  $V_{DD}$  = +12V  $\pm 5\%$  ,  $V_{CC}$  = +5V  $\pm 5\%$  ,  $V_{BB}$  = -5V  $\pm 5\%$  , GRDA = 0V, GRDD = 0V, unless otherwise specified.

#### **TRANSMISSION**

| Symbol           | Parameter                                                                           | umeter Limits Un |                        | Unit                   | Test Conditions |                                                                                                                                                                                                                                                                                       |

|------------------|-------------------------------------------------------------------------------------|------------------|------------------------|------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | raiametei                                                                           | Min              | <b>Typ</b> (1)         | Max                    |                 |                                                                                                                                                                                                                                                                                       |

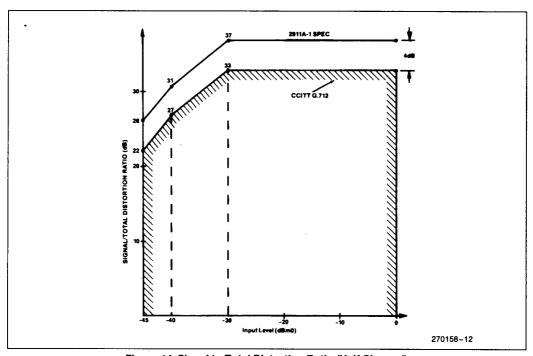

| S/D              | Signal to Total Distortion Ratio.<br>CCITT G.712 Method 2                           | 37               |                        |                        | dB              | Signal level 0 dBm0 to<br>-30 dBm0                                                                                                                                                                                                                                                    |

|                  | (Half Channel)                                                                      | 31               |                        |                        | dΒ              | Signal level to -40 dBm0                                                                                                                                                                                                                                                              |

|                  |                                                                                     | 26               |                        |                        | dΒ              | Signal level to -45 dBm0                                                                                                                                                                                                                                                              |

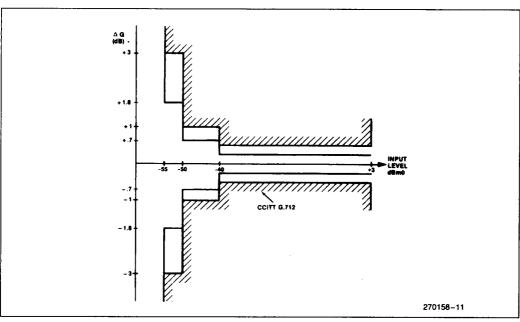

| ΔG               | 2911A Gain Tracking Deviation Half Channel <sup>(3)</sup> Reference Level - 10 dBm0 |                  | ±0.25<br>±0.60<br>±1.5 | ±0.30<br>±0.70<br>±1.8 | dB<br>dB<br>dB  | $\begin{array}{l} \text{VF}_{\text{X}} = 1.02 \text{ KHz, sinusoid} \\ -40 \text{ dBm0} \leq \text{VF}_{\text{X}} \leq +3 \text{ dBm0} \\ -50 \text{ dBm0} \leq \text{VF}_{\text{X}} < -40 \text{ dBm0} \\ -55 \text{ dBm0} \leq \text{VF}_{\text{X}} < -50 \text{ dBm0} \end{array}$ |

| $\Delta G_V$     | ΔG Variation with Supplies<br>Half Channel                                          |                  | ±0.0002<br>±0.0004     |                        |                 | $\begin{array}{l} -40~\text{dBm0} \leq \text{VF}_{\text{X}} \leq +3~\text{dBm0} \\ -50~\text{dBm0} \leq \text{VF}_{\text{X}} < -40~\text{dBm0} \end{array}$                                                                                                                           |

| ΔG <sub>T</sub>  | ΔG Variation with<br>Temperature Half Channel                                       |                  | ±0.001<br>±0.002       | ±0.002<br>±0.005       | dB/°C           | $\begin{array}{l} -40~\text{dBm0} \leq \text{VF}_{\text{X}} \leq +3~\text{dBm0} \\ -50~\text{dBm0} \leq \text{VF}_{\text{X}} < -40~\text{dBm0} \end{array}$                                                                                                                           |

| N <sub>IC</sub>  | Idle Channel Noise                                                                  |                  | -85                    | -78                    | dBm0p           | Quiet Code. (Note 2)                                                                                                                                                                                                                                                                  |

| HD               | Harmonic Distortion<br>(2nd or 3rd)                                                 |                  | -48                    | - 44                   | dB              | VF <sub>X</sub> = 1.02 KHz, 0 dBm0;<br>measured at decoder output VF <sub>R</sub>                                                                                                                                                                                                     |

| IMD <sub>1</sub> | Intermodulation Distortion<br>G.712(7.1)<br>G.712(7.2)                              |                  |                        | -45<br>-50             | dB<br>dBm0      | CCITT G.712<br>Two Tone Method                                                                                                                                                                                                                                                        |

<sup>1.</sup> Typical values are for  $T_A = 25^{\circ}C$  and nominal power supply values.

#### A.C. CHARACTERISTICS

$T_A = 0^{\circ}$ C to  $+70^{\circ}$ C,  $V_{DD} = +12$ V  $\pm 5\%$ ,  $V_{CC} = +5$ V  $\pm 5\%$ ,  $V_{BB} = -5$ V  $\pm 5\%$ , GRDA = 0V, GRDD = 0V, unless otherwise specified. (Continued)

#### **GAIN AND DYNAMIC RANGE**

| Symbol           | Parameter                                   |       | Limits |        | Unit                  | Test Conditions                                                    |  |

|------------------|---------------------------------------------|-------|--------|--------|-----------------------|--------------------------------------------------------------------|--|

| Symbol           | Farameter                                   | Min   | Typ(1) | Max    | Oille                 | rest Conditions                                                    |  |

| DmW              | Digital Milliwatt Response                  | 5.58  | 5.66   | 5.78   | dBm                   | 23°C, nominal supplies(4)                                          |  |

| DmW <sub>T</sub> | DmW <sub>O</sub> Variation with Temperature |       | -0.001 | -0.002 | dB/°C                 | Relative to 23°C(4)                                                |  |

| DmW <sub>S</sub> | DmW <sub>O</sub> Variation with Supplies    |       |        | ±0.07  | dB                    | Supplies ±5%(4)                                                    |  |

| A <sub>IR</sub>  | Input Dynamic Range                         | 2.183 | 2.213  | 2.243  | V <sub>RMS</sub>      | Using D.C. and A.C. tests <sup>(5)</sup><br>23°C, nominal supplies |  |

| A <sub>IRT</sub> | Input Dynamic Range vs Temperature          |       |        | -0.5   | mV <sub>RMS</sub> /°C | Relative to 23°C                                                   |  |

| A <sub>IRS</sub> | Input Dynamic Range vs Supplies             |       |        | ±18    | mV <sub>RMS</sub>     | Supplies ±5%                                                       |  |

| A <sub>OR</sub>  | Output Dynamic Range,<br>VF <sub>R</sub>    | 2.14  | 2.17   | 2.20   | V <sub>RMS</sub>      | 23°C, Nominal Supplies                                             |  |

| AORT             | A <sub>OR</sub> Variation with Temperature  |       |        | -0.5   | mV <sub>RMS</sub> /°C | Relative to 23°C                                                   |  |

| A <sub>ORS</sub> | A <sub>OR</sub> Variation with Supplies     |       |        | ± 18   | mV <sub>RMS</sub>     | Supplies ±5%                                                       |  |

#### SUPPLY REJECTION AND CROSSTALK

| Symbol            | Parameter                                    |      | Limits |      | Unit | Test Conditions              |

|-------------------|----------------------------------------------|------|--------|------|------|------------------------------|

|                   | rarameter                                    | Min  | Typ(1) | Max  |      | rest Conditions              |

| PSRR <sub>1</sub> | V <sub>DD</sub> Power Supply Rejection Ratio | 45   |        |      | dB   | decoder alone(6)             |

| PSRR <sub>2</sub> | V <sub>BB</sub> Power Supply Rejection Ratio | 35   |        |      | dB   | decoder alone(6)             |

| PSRR <sub>3</sub> | V <sub>CC</sub> Power Supply Rejection Ratio | 50   |        |      | dB   | decoder alone(6)             |

| PSRR <sub>4</sub> | V <sub>DD</sub> Power Supply Rejection Ratio | 50   |        |      | dΒ   | encoder alone <sup>(7)</sup> |

| PSRR <sub>5</sub> | V <sub>BB</sub> Power Supply Rejection Ratio | 45   |        |      | dB   | encoder alone <sup>(7)</sup> |

| PSRR <sub>6</sub> | V <sub>CC</sub> Power Supply Rejection Ratio | 50   |        |      | ₫B   | encoder alone <sup>(7)</sup> |

| CTR               | Crosstalk Isolation, Receive Side            | 75   | 80     |      | dB   | (Note 8)                     |

| CTT               | Crosstalk Isolation, Transmit Side           | 75   | 80     |      | dB   | (Note 9)                     |

| CAPX              | Input Sample and Hold Capacitor              | 1600 | 2000   | 2400 | pF   |                              |

#### NOTES

- 1. Typical values are for  $T_A = 25^{\circ}C$  and nominal power supply values.

- 2. If the external auto zero is used N<sub>IC</sub> has a typical value of -76 dBm0.

- 3. Tested and guaranteed at 23°C, nominal supplies.

- 4. D<sub>R</sub> of Device Under Test (D.U.T.) driven with repetitive digital word sequence specified in CCITT recommendation G.711. Measurement made at VF<sub>R</sub> output.

- 5. With the D.C. method the positive and negative clipping levels are measured and  $A_{IR}$  is calculated. With the A.C. method a sinusoidal input signal to  $VF_X$  is used where  $A_{IR}$  is measured directly.

- 6. D.U.T. decoder; impose 200 mV<sub>PP</sub>, 1.02 KHz on appropriate supply; measurement made at decoder output; decoder in idle channel conditions.

- 7. D.U.T. encoder, impose 200 mV<sub>PP</sub>, 1.02 KHz on appropriate supply; meaurement made at encoder output; encoder in idle channel conditions.

- 8.  $VF_X$  of D.U.T encoder = 1.02 KHz, 0 dBm0. Decoder under quiet channel conditions; measurements made at decoder output.

- 9.  $\dot{V}F_{\chi}$  = 0 Vrms. Decoder = 1.02 KHz, 0 dBm0. Encoder under quiet channel conditions; measurement made at encoder output.

Figure 13. Tracking Deviation ( $\Delta$ G) (Half Channel)

Figure 14. Signal to Total Distortion Ratio (Half Channel)

# A.C. CHARACTERISTICS—TIMING SPECIFICATION(1)

$T_A = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{DD} = +12V \pm 5\%$ ,  $V_{CC} = +5V \pm 5\%$ ,  $V_{BB} = -5V \pm 5\%$ , GRDA = 0V, GRDD = 0V, unless otherwise specified.

#### **CLOCK SECTION**

| Symbol                          | Parameter                                              | Limits |     | 11-14 | 0                                                                         |

|---------------------------------|--------------------------------------------------------|--------|-----|-------|---------------------------------------------------------------------------|

|                                 |                                                        | Min    | Max | Unit  | Comments                                                                  |

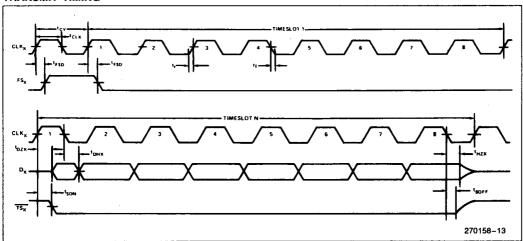

| tcy                             | Clock Period                                           | 485    |     | ns    | CLK <sub>X</sub> , CLK <sub>R</sub> (2.048 MHz systems), CLK <sub>C</sub> |

| t <sub>r</sub> , t <sub>f</sub> | Clock Rise and Fall Time                               | 0      | 30  | ns    | CLK <sub>X</sub> , CLK <sub>R</sub> , CLK <sub>C</sub>                    |

| t <sub>CLK</sub>                | Clock Pulse Width                                      | 215    |     | ns    | CLK <sub>X</sub> , CLK <sub>R</sub> , CLK <sub>C</sub>                    |

| tcpc                            | Clock Duty Cycle (t <sub>CLK</sub> + t <sub>CY</sub> ) | 45     | 55  | %     | CLK <sub>X</sub> , CLK <sub>R</sub>                                       |

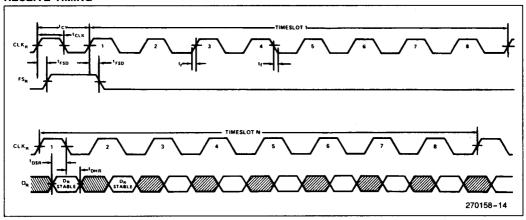

#### TRANSMIT SECTION

| Symbol           | Parameter                | Limits |     | 14-14    | 0                                         |

|------------------|--------------------------|--------|-----|----------|-------------------------------------------|

|                  |                          | Min    | Max | Unit     | Comments                                  |

| t <sub>VFX</sub> | Analog Input Conversion  | 20     |     | Timeslot | From Leading Edge of Transmit Timeslot(2) |

| t <sub>DZX</sub> | Data Enabled on TS Entry | 50     | 180 | ns       | 0 < C <sub>LOAD</sub> < 100 pF            |

| t <sub>DHX</sub> | Data Hold Time           | 80     | 230 | ns       | 0 < C <sub>LOAD</sub> < 100 pF            |

| tHZX             | Data Float on TS Exit    | 75     | 245 | ns       | C <sub>LOAD</sub> = 0                     |

| tson             | Timeslot X to Enable     | 30     | 185 | ns       | 0 < C <sub>LOAD</sub> < 100 pF            |

| tsoff            | Timeslot X to Disable    | 70     | 225 | ns       | $C_{LOAD} = 0$                            |

| t <sub>FSD</sub> | Frame Sync Delay         | 15     | 150 | ns       |                                           |

#### **RECEIVE AND CONTROL SECTIONS**

| Symbol           | Parameter            | Limits |       | Unit     | 2                                         |

|------------------|----------------------|--------|-------|----------|-------------------------------------------|

|                  |                      | Min    | Max   | Unit     | Comments                                  |

| t <sub>VFR</sub> | Analog Output Update | 91/16  | 91/16 | Timeslot | From Leading Edge of the Channel Timeslot |

| t <sub>DSR</sub> | Receive Data Setup   | 20     |       | ns       |                                           |

| tohr             | Receive Data Hold    | 60     |       | ns       |                                           |

| t <sub>FSD</sub> | Frame Sync Delay     | 15     | 150   | ns       |                                           |

| t <sub>DSC</sub> | Control Data Setup   | 115    |       | ns       | Microcomputer Mode Only                   |

| tDHC             | Control Data Hold    | 115    |       | ns       | Microcomputer Mode Only                   |

All timing parameters referenced to 1.5V, except t<sub>HZX</sub> and t<sub>SOFF</sub>, which reference a high impedance state.

The 20 timeslot minimum insures that the complete A/D conversion will take place under any combination of receive interrupt or asynchronous operation of the Codec. Consult an Intel applications specialist or Intel Corporation for applications information which would allow operation with less than 20 timeslots.

# TIMING WAVEFORMS(1)

#### TRANSMIT TIMING

#### **RECEIVE TIMING**

#### **CONTROL TIMING**

#### NOTE:

1. All timing parameters referenced to 1.5V, except tHZX and tSOFF which reference a high impedance state.