# TLC10/MF10A, TLC20/MF10C

D2952, AUGUST 1986-REVISED NOVEMBER 1988

Maximum Clock to Center-Frequency Ratio

Error

TLC10 . . . ± 0.6% TLC20 . . . ± 1.5%

- Filter Cutoff Frequency Stability Dependent Only on External-Clock Frequency Stability

- Minimum Filter Response Deviation Due to External Component Variations over Time and Temperature

- Critical-Frequency Times Q Factor Range Up to 200 kHz

- Critical-Frequency Operation Up to 30 kHz

- Designed to be Interchangeable with: National MF10

Maxim MF10

Linear Technology LTC1060

#### description

The TLC10/MF10A and TLC20/MF10C are monolithic general-purpose switched-capacitor CMOS filters each containing two independent active-filter sections. Each device facilitates configuration of Butterworth, Bessel, Cauer, or Chebyshev filter design.

Filter features include cutoff frequency stability that is dependent only on the external clock frequency stability and minimal response deviation over time and temperature. Features also include a critical-frequency times filter quality (Q) factor range of up to 200 kHz.

With external clock and resistors, each filter section can be used independently to produce various second-order functions or both sections can be cascaded to produce fourth-order functions. For functions greater than fourth-order, ICs can be cascaded.

The TLC10/MF10A and TLC20/MF10C are characterized for operation from 0 °C to 70 °C.

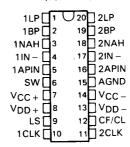

# N DUAL-IN-LINE PACKAGE (TOP VIEW)

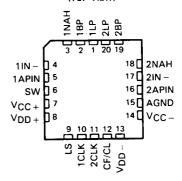

# FN CHIP CARRIER PACKAGE (TOP VIEW)

#### **AVAILABLE OPTIONS**

|                   |                                     | PACKAGE              |             |  |  |  |  |  |

|-------------------|-------------------------------------|----------------------|-------------|--|--|--|--|--|

| TA                | MAX<br>f <sub>clock</sub> /fc ERROR | CHIP CARRIER<br>(FN) | PLASTIC DIF |  |  |  |  |  |

|                   |                                     | TLC10CFN             | TLC10CN     |  |  |  |  |  |

|                   | ±0.6%                               | or                   | or          |  |  |  |  |  |

| 0°C<br>to<br>70°C |                                     | MF10ACFN             | MF10ACN     |  |  |  |  |  |

|                   |                                     | TLC20CFN             | TLC20CN     |  |  |  |  |  |

|                   | ± 1.5%                              | or                   | or          |  |  |  |  |  |

|                   |                                     | MF10CCFN             | MF10CCN     |  |  |  |  |  |

### TLC10/MF10A, TLC20/MF10C UNIVERSAL DUAL SWITCHED-CAPACITOR FILTER

| PIN               | ı        | Γ        |                                                                                                                                |

|-------------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------|

| NAME              | NO.      | 1/0      | DESCRIPTION                                                                                                                    |

| AGND              | 15       | T        | Analog Ground — The noninverting inputs to the input operational amplifiers of both filter sections. This terminal             |

|                   |          | L        | should be at ground for dual supplies or at mid-supply level for single-supply operation.                                      |

| 1APIN             | 5        | T        | All-Pass Inputs — The all-pass input to the summing amplifier of each respective filter section used for all-pass              |

| 2APIN             | 16       |          | filter applications in configuration modes 1a, 4, 5, and 6. This terminal should be driven from a source having                |

| L                 |          | <u> </u> | an impedance of less than 1 k $\Omega$ . In all other modes, this terminal is grounded. See Typical Application Data.          |

| 1BP               | 2        | 0        | Band-Pass Outputs — The band-pass output of each respective filter section provides the second-order band-                     |

| 2BP               | 19       | Ĺ        | pass filter functions.                                                                                                         |

| CF/CL             | 12       | 1        | Center Frequency/Current Limit — This input terminal provides the option to select the input-clock-to-center-                  |

|                   |          |          | frequency ratio of 50:1 or 100:1 or to limit the current of the IC. For a 50:1 ratio, the CF/CL terminal is set                |

|                   |          | i        | to VDD+. For a 100:1 ratio, the CF/CL terminal is set to ground for dual supplies or to mid-supply level for                   |

|                   | ĺ        |          | single-supply operation. For current limiting, the CF/CL terminal is set to V <sub>DD</sub> . This aborts filtering and limits |

|                   |          | <u> </u> | the IC current to 0.5 milliamperes.                                                                                            |

| 1CLK              | 10       | 1        | Clock Inputs - The clock input to the two-phase nonoverlapping generator of each respective filter section                     |

| 2CLK              | .11      |          | is used to generate the center frequency of the complex pole pair second-order function. Both clocks should                    |

|                   |          |          | be of the same level (TTL or CMOS) and have duty cycles close to 50%, especially when clock frequencies                        |

|                   |          |          | (fclock) greater than 200 kHz are used. At this duty cycle, the operational amplifiers have the maximum time                   |

| Ĺ                 | <u> </u> |          | to settle while processing analog samples.                                                                                     |

| 1IN –             | 4        | 1        | Inverting Inputs — The inverting input side of the input operational amplifier whose output drives the summing                 |

| 2IN -             | 17       |          | amplifier of each respective filter section.                                                                                   |

| 1LP               | 1        | 0        | Low-Pass Outputs — The low-pass outputs of the second-order filters.                                                           |

| 2LP               | 20       |          |                                                                                                                                |

| LS                | 9        | 1        | Level Shift — This terminal accommodates various input clock levels of bipolar (CMOS) or unipolar (TTL or                      |

|                   |          |          | other clocks) to function with single or dual supplies. For CMOS (±5-volt) clocks, Vpp = or ground is applied                  |

| 151511            |          |          | to the LS terminal. For TTL and other clocks, ground is applied to the LS terminal.                                            |

| 1NAH<br>2NAH      | 3<br>18  | 0        | Notch, All-Pass, or High-Pass Outputs — The output of each respective filter section can be used to provide                    |

| SW                |          |          | either a second-order notch, all-pass, or high-pass output filter function, depending on circuit configuration                 |

| 300               | 6        | ' 1      | Switch Input — This input terminal is used to control internal switches to connect either the AGND input or                    |

|                   | ľ        | ļ        | the LP output to one of the inputs of the summing amplifier. The terminal controls both independent filter sections            |

| ł                 |          |          | and places them in the same configuration simultaneously. If VCC - is applied to the SW terminal, the AGND                     |

| ,                 |          |          | imput terminar will be connected to one of the inputs of each summing amplifier. If Vcc., is applied to the                    |

| - Van             | 7        |          | over terminar, the LP output will be connected to one of the inputs of the summing amplifier.                                  |

| V <sub>CC+</sub>  | 14       | -        | Analog positive supply voltage terminal                                                                                        |

| VCC-              | 8        |          | Analog negative supply voltage terminal                                                                                        |

| V <sub>DD+</sub>  | 13       |          | Digital positive supply voltage terminal                                                                                       |

| V <sub>DD</sub> – | 13       |          | Digital negative supply voltage terminal                                                                                       |

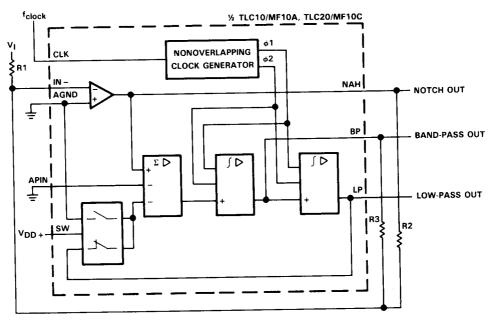

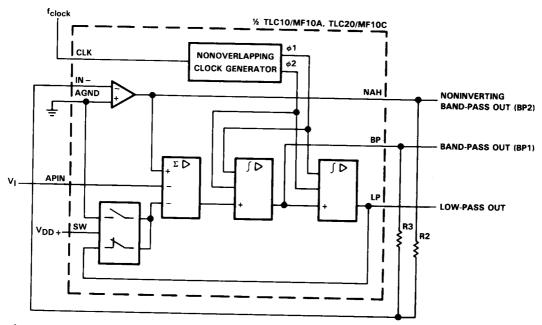

### functional block diagram 1CLK (10) LS (9) NONOVERLAPPING φ2 CF/CL (12) CLOCK GENERATOR CONTROL IN - (4) (3) 1NAH AGND (15) (2) 1BP SD ΣD SD 1APIN (5) (1) 1LP sw (6) 2CLK (11) NONOVERLAPPING φ2 CLOCK GENERATOR CONTROL 2IN - (17) (18) 2NAH (<u>19)</u> 2BP **S D** ΣD SD 2APIN (16) (20) 2LP

### TLC10/MF10A, TLC20/MF10C UNIVERSAL DUAL SWITCHED-CAPACITOR FILTER

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Analog supply voltage, VCC± (see Note 1)                                      | .,     |

|-------------------------------------------------------------------------------|--------|

| Digital supply voltage, VDD+                                                  | V      |

| Digital supply voltage, VDD ± ± 7 V                                           | ٧      |

| 00C +0 700                                                                    | $\sim$ |

| ctorage temperature range                                                     | _      |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: FN or N package | c      |

NOTE 1: All voltage values are with respect to the AGND terminal.

### recommended operating conditions

| Analog cure live IV                                     | MIN   | NOM | MAX | UNIT |

|---------------------------------------------------------|-------|-----|-----|------|

| Analog supply voltage, V <sub>CC±</sub> , (see Note 2)  | ±4    | ±5  | ±6  | V    |

| Digital supply voltage, V <sub>DD±</sub> , (see Note 2) | ± 4   | ±5  | ± 6 | V    |

| Clock frequency, f <sub>clock</sub> , (see Note 3)      | 0.008 |     | 1.0 | MHz  |

| Operating free-air temperature, TA                      | 0     |     | 70  | °C   |

NOTES: 2. A common supply voltage source should be used for the analog and digital supply voltages. Although each has separate terminals, they are connected together internally at the substrate. V<sub>CC</sub> + and V<sub>DD</sub> + can be connected together at the device terminals or at the supply voltage source. The same is true for V<sub>CC</sub> - and V<sub>DD</sub> -.

3. Both input clocks should be of the same level type (TTL or CMOS), and their duty cycles should be at 50% above 200 kHz to allow the operational amplifiers the maximum time to settle while processing analog samples.

# electrical characteristics at $V_{CC\pm} = \pm 5 \text{ V}$ , $V_{DD\pm} + = \pm 5 \text{ V}$ , $T_A = 25 \text{ °C}$ (unless otherwise noted)

| PARAMETER                   |                        |        | TEST CONDITIONS                        | TLC10/MF10A |      |     | TLC20/MF10C |       |             |      |

|-----------------------------|------------------------|--------|----------------------------------------|-------------|------|-----|-------------|-------|-------------|------|

|                             |                        |        | N N                                    |             | TYP  | MAX | MIN         | TYP   | MAX         | UNIT |

| Maximum peak-to-peak output |                        |        |                                        |             |      |     |             |       | <del></del> |      |

| TOPP                        | voltage swing          |        | R <sub>L</sub> = 3.5 kΩ at all outputs | ±4          | ±4.1 |     | ±3.8        | ± 3.9 |             | V    |

| loo                         | Short-circuit output   | Source | _                                      |             | 2    |     |             |       |             |      |

| 10\$                        | current, Pins 3 and 18 | Sink   | See Note 4                             |             |      |     |             |       |             | mA   |

| lcc                         | Supply current         | J.IIK  |                                        | <b></b>     | 50   |     |             | 50    |             |      |

| -00_                        | Supply Culterit        |        | L                                      |             | 8    | 10  |             | 8     | 10          | mA   |

NOTE 4: The short-circuit output current for pins 1, 2, 19, and 20 will be typically the same as pins 3 and 18.

# operating characteristics at $V_{CC\pm} = \pm 5 \text{ V}$ , $V_{DD\pm} = \pm 5 \text{ V}$ , $T_A = 25 \,^{\circ}\text{C}$ (unless otherwise noted)

| PARAMETER                                      | TEST CONDITIONS        |               | TLC10/MF10A                    |               |       | TLC20/MF10C |       |       |        |          |

|------------------------------------------------|------------------------|---------------|--------------------------------|---------------|-------|-------------|-------|-------|--------|----------|

| 0.111.111                                      |                        |               |                                | MIN           | TYP   | MAX         | MIN   | TYP   | MAX    | UNIT     |

| Critical-frequency range                       | $f_0 \times Q \leq 20$ | 00 kHz        |                                | 20            | 30    |             | 20    | 30    |        | kHz      |

| Maximum clock<br>frequency, f <sub>clock</sub> | See Note 3             |               |                                | 1             | 1.5   |             | 1     | 1.5   |        | MHz      |

| Clock to center-frequency ratio                |                        |               | Pin 12 at 5 V                  | 49.64         | 49.94 | 50.24       | 49.24 | 49.94 | 50.64  | <u> </u> |

| Temperature coefficient of                     |                        |               | Pin 12 at 0 V<br>Pin 12 at 5 V | 98.75         | 99.35 | 99.95       | 97.86 | 99.35 | 100.84 |          |

| center frequency                               | Mode 1,                |               | Pin 12 at 5 V                  | -             | ± 10  |             | ļ     | ± 10  |        | ppm/°C   |

| Filter Q (quality factor)                      |                        |               | Pin 12 at 5 V                  | <del></del> - | ± 100 |             |       | ± 100 |        | ррін, с  |

| deviation from 20                              | Mode 1,                |               |                                |               | ± 2%  | ± 4%        |       | ± 2%  | ±6%    |          |

| Temperature coefficient of                     | <del></del>            | R3/R2 = 20,   | Pin 12 at 0 V                  |               | ± 2%  | ± 3%        |       | ± 2%  | ±6%    |          |

| measured filter Q                              | Mode 1                 | 110/112 4 20, |                                |               | ± 500 |             |       | ± 500 |        | ppm/°C   |

| Low-pass output deviation                      | R1 = R2 =              | 0 kΩ          |                                |               |       |             |       |       |        | <u> </u> |

| from unity gain                                | Mode 1,                | See Figure 1  |                                |               |       | ± 2%        |       |       | ± 2%   |          |

| Crosstalk attenuation                          |                        |               |                                |               | 60    |             |       | 60    |        |          |

| Clock feedthrough voltage                      |                        |               |                                |               | 10    |             |       |       |        | dB       |

| Operational amplifier                          |                        |               |                                |               |       |             |       | 10    |        | mV       |

| gain-bandwidth product                         |                        |               |                                |               | 2.5   |             |       | 2.5   |        | MHz      |

| Operational amplifier                          |                        |               |                                |               |       |             |       |       |        |          |

| slew rate                                      |                        |               |                                |               | 7     |             |       | 7     |        | V/μs     |

#### modes of operation

The TLC10/MF10A and TLC20/MF10C are switched-capacitor (sampled-data) filters that closely approximate continuous filters. Each filter section is designed to approximate the response of a secondorder variable filter. When the sampling frequency is much larger than the frequency band of interest, the sampled-data filter is a good approximation to its continuous time equivalent. In the case of the TLC10/MF10A and TLC20/MF10C, the ratio is about 50:1 or 100:1. To fully describe their transfer function, a time domain approach would be appropriate. Since this may appear cumbersome, the following application examples are based on the well known frequency domain. It should be noted that in order to obtain the actual filter response, the filter's response must be examined in the z-domain.

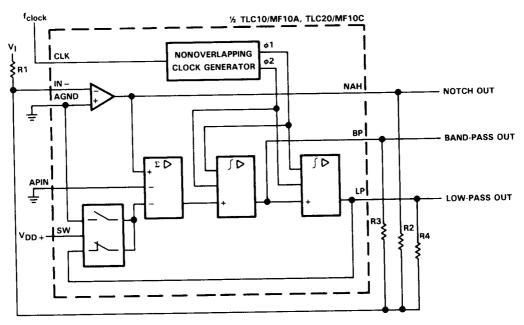

```

f_0 = f_{clock}/100 \text{ or } f_{clock}/50

f_{notch} = f_{o}

H_{OLP} = -R2/R1 \text{ (as f} \rightarrow 0)

H_{OBP} = -R3/R1 (at f = f_0)

HON = notch gain as f approaches 0 - R2/R1 as f approaches 0.5 fclock

Q = f_0/BW = R3/R2

```

Circuit dynamics:

The following expressions determine the swing at each output as a function of the desired Q of the second-order function.  $H_{OLP} = H_{OBP}/Q$  or  $H_{OLP} \times Q = H_{ON} \times Q$ HOLP (peak) = Q × HOLP (for high Qs)

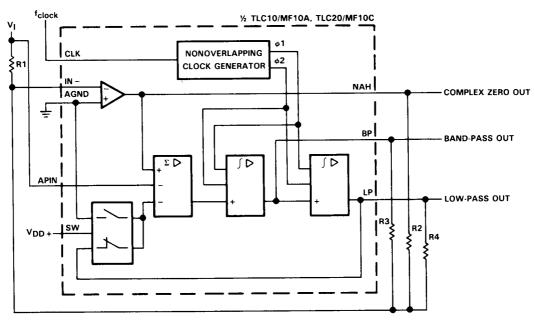

FIGURE 1. MODE 1 FOR NOTCH, BAND-PASS, AND LOW-PASS OUTPUTS: fnotch = fo

$f_0 = f_{clock}/100 \text{ or } f_{clock}/50$  Q = R3/R2

$H_{OLP} = -1$   $H_{OLP}$  (peak) = Q ×  $H_{OLP}$  (for high Qs)

$H_{OBP1} = -R3/R2$

HOBP2 = 1 (noninverting)

Circuit dynamics:

$H_{OBP1} = Q$

FIGURE 2. MODE 1a FOR NONINVERTING BAND-PASS AND LOW-PASS OUTPUTS

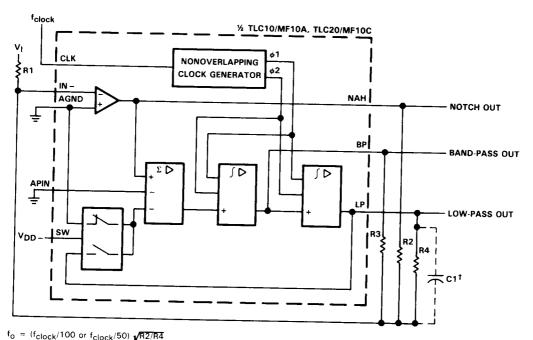

$$\begin{array}{l} f_0 = f_{notch} \times \sqrt{R2/R4 + 1} \\ f_{notch} = f_{clock}/100 \text{ or } f_{clock}/50 \\ \Omega = \sqrt{\frac{R2/R4 + 1}{R2/R3}} \\ H_{OLP} \text{ (as f approaches 0)} = \frac{-R2/R1}{R2/R4 + 1} \\ H_{OBP} \text{ (at f = f_0)} = -R3/R1 \\ H_{ON1} \text{ (as f approaches 0)} = \frac{-R2/R1}{R2/R4 + 1} \\ H_{ON2} \text{ (as f approaches 0.5 } f_{clock}) = -R2/R1 \\ \text{Circuit dynamics:} \\ H_{OBP} = \Omega \sqrt{H_{OLP} \times H_{ON2}} = \Omega \sqrt{H_{ON1} \times H_{ON2}} \end{array}$$

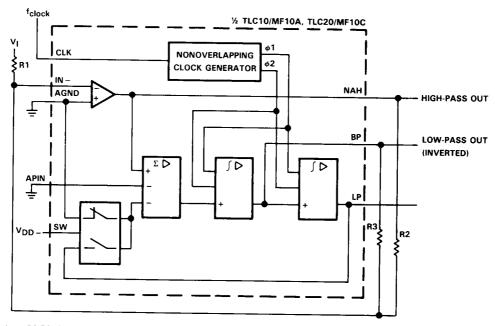

FIGURE 3. MODE 2 FOR NOTCH 2, BAND-PASS, AND LOW-PASS OUTPUTS:  $f_{notch} \ \langle \ f_{o} \ \rangle$

```

Q = \sqrt{R2/R4} \times R3/R2

HOHP (as f approaches 0.5 f_{clock}) = -R2/R1

HOLP (as f approaches 0) = -R4/R1

HOBP (at f = f_0) = -R3/R1

Circuit dynamics:

R2/R4 = HOHP/HOLP: HOBP = \sqrt{HOHP \times HOLP} \times Q

HOLP (peak) = Q \times HOLP (for high Qs)

HOHP (peak) = Q \times HOHP (for high Qs)

```

FIGURE 4. MODE 3 FOR HIGH-PASS, BAND-PASS, AND LOW-PASS OUTPUTS

<sup>†</sup>In this mode, the feedback loop is closed around the input summing amplifier; the finite GBW product of this operational amplifier will cause a slight Q enhancement. If this is a problem, connect a low-value capacitor (10 pF to 100 pF) across R4 to provide some phase lead.

```

f_0 = (f_{clock}/100 \text{ or } f_{clock}/50) \sqrt{R2/R4}

```

$Q = \sqrt{R2/R4} \times R3/R2$

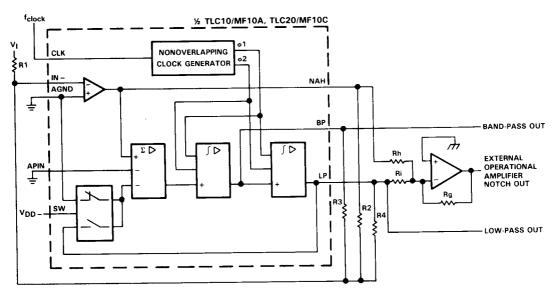

$H_{OHP} = -R2/R1$

$H_{OBP} = -R3/R1$

$H_{OLP} = -R4/R1$

$f_{notch} = (f_{clock}/100 \text{ or } f_{clock}/50) \sqrt{Rh/Ri}$

$H_{ON}$  (at f = f<sub>O</sub>) = | Q (Rg/Ri ×  $H_{OLP}$  - Rg/Rh × HOHP) |

$H_{ON1}$  (as f approaches 0) =  $Rg/Ri \times H_{OLP}$

$H_{ON2}$  (as f approaches 0.5  $f_{clock}$ ) =  $-Rg/Rh \times H_{OHP}$

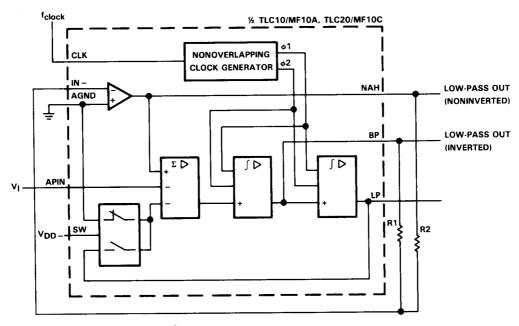

FIGURE 5. MODE 3a FOR HIGH-PASS, BAND-PASS, LOW-PASS, AND NOTCH OUTPUTS WITH EXTERNAL OPERATIONAL AMPLIFIER

8-23

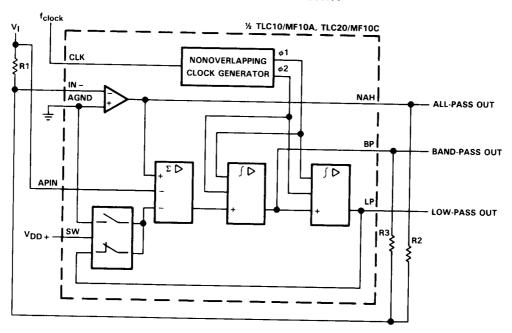

```

\begin{array}{l} f_{O} = f_{clock}/100 \text{ or } f_{clock}/50 \\ f_{Z} = f_{O}^{-1} \\ Q = f_{O}/BW = R3/R2 \\ Q_{Z} = R3/R1 \\ HOAP (at <math>0 \leq f \leq 0.5 \ f_{clock}) = -R2/R1 = -1 \\ (for AP output R1 = R2) \\ HOLP (as f approaches <math>0) = -(R2/R1 + 1) = -2 \\ HOBP (at <math>f = f_{O}) = -R3/R2 \ (R2/R1 + 1) = -2 \ (R3/R2) \\ Circuit dynamics: \\ HOBP = HOLP \times Q = (HOAP + 1) \ Q \end{array}

```

FIGURE 6. MODE 4 FOR ALL-PASS, BAND-PASS, AND LOW-PASS OUTPUTS

$<sup>^{\</sup>dagger}$ Due to the sampled-data nature of the filter, a slight mismatch of  $f_z$  and  $f_0$  occurs causing a 0.4-dB peaking around  $f_0$  of the all-pass filter amplitude response (which theoretically should be a straight line). If this is unacceptable, Mode 5 is recommended.

```

\begin{array}{lll} f_0 &=& \sqrt{R2/R4 \,+\, 1} \,\times\, (f_{clock}/100 \,\, or \,\, f_{clock}/50) \\ f_Z &=& \sqrt{1 \,-\, R1/R4} \,\times\, (f_{clock}/100 \,\, or \,\, f_{clock}/50) \\ Q &=& \sqrt{R2/R4 \,+\, 1} \,\times\, R3/R2 \\ Q_Z &=& \sqrt{1 \,-\, R1/R4} \,\times\, R3/R1 \\ H_{OZ1} \,(as \,f \,approaches \, 0) &=& R2 \,(R4 \,-\, R1)/R1 \,(R2 \,+\, R4) \\ H_{OZ2} \,(as \,f \,approaches \, 0.5 \,\, f_{clock}) &=& R2/R1 \\ H_{OBP} &=& (R2/R1 \,+\, 1) \,\times\, R3/R2 \\ H_{OLP} &=& (R2 \,+\, R1)/(R2 \,+\, R4) \,\times\, R4/R1 \\ \end{array}

```

FIGURE 7. MODE 5 FOR NUMERATOR COMPLEX ZEROS, BAND-PASS, AND LOW-PASS OUTPUTS

$f_C = R2/R3 \{f_{clock}/100 \text{ or } f_{clock}/50\}$

$H_{OLP} = -R3/R1$

$H_{OHP} = -R2/R1$

FIGURE 8. MODE 6 FOR SINGLE-POLE HIGH-PASS AND LOW-PASS OUTPUT

$f_C = R2/R3 \times (f_{clock}/100 \text{ or } f_{clock}/50)$

HOLP1 = 1 (noninverting)

$\mathsf{H}_{OLP2} \ = \ -\,\mathsf{R3/R2}$

FIGURE 9. MODE 6a FOR SINGLE-POLE LOW-PASS OUTPUT (INVERTED AND NONINVERTED)

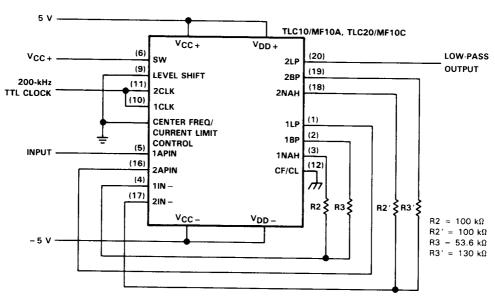

FIGURE 10. FOURTH-ORDER 2-kHz LOW-PASS BUTTERWORTH FILTER

#### filter terminology

| $f_{C}$            | The cutoff frequency of the low-pass or high-pass filter output                                                                               |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| <sup>f</sup> clock | The input clock frequency to the device                                                                                                       |

| fnotch             | The notch frequency of the notch output                                                                                                       |

| $f_{O}$            | The center frequency of the complex pole pair second-order function                                                                           |

| f <sub>z</sub>     | The center frequency of the complex zero pair                                                                                                 |

| HOBP               | The band-pass output voltage gain (V/V) at the band-pass center frequency                                                                     |

| HOHP               | The high-pass output voltage gain (V/V) as the frequency approaches 0.5 folcok                                                                |

| HOLP               | The low-pass output voltage gain (V/V) as the frequency approaches 0                                                                          |

| HON                | The notch output voltage gain (V/V) at the notch frequency                                                                                    |

| HON1               | The low-side notch output voltage gain as the frequency approaches 0                                                                          |

| HON2               | The high-side notch output voltage gain as the frequency approaches 0.5 fclock                                                                |

| HOZ1               | Gain at complex zero output (as f $\rightarrow$ 0 Hz)                                                                                         |

| HOZ2               | Gain at complex zero output (as f approaches 0.5 fclock)                                                                                      |

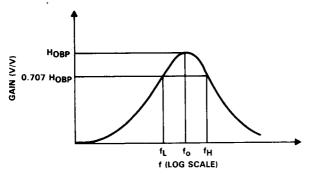

| Q                  | The quality factor of the complex pole pair second-order function. Q is the ratio of fo to                                                    |

|                    | the 3-dB bandwidth of the band-pass output. The value of Q also affects the possible                                                          |

| _                  | peaking of the low-pass and high-pass outputs.                                                                                                |

| $Q_z$              | The quality factor of the complex zero pair, if such a complex pair exists. This parameter is used when an all-pass filter output is desired. |

$$Q = \frac{f_0}{f_H - f_L}; f_0 = \sqrt{f_L f_H}$$

$$f_L = f_0 \left(\frac{-1}{2Q} + \sqrt{\left(\frac{1}{2Q}\right)^2 + 1}\right)$$

$$f_H = f_0 \left(\frac{1}{2Q} + \sqrt{\left(\frac{1}{2Q}\right)^2 + 1}\right)$$

FIGURE 11. BAND-PASS OUTPUT

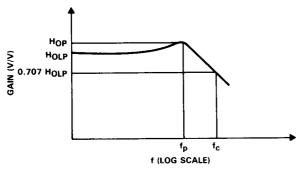

$$f_{c} = f_{o} \times \sqrt{\left(1 - \frac{1}{2Q^{2}}\right) + \sqrt{\left(1 - \frac{1}{2Q^{2}}\right)^{2} + 1}}$$

$$f_{p} = f_{o} \sqrt{1 - \frac{1}{2Q^{2}}}$$

$$H_{OP} = H_{OLP} \times \frac{1}{\frac{1}{Q}\sqrt{1 - \frac{1}{4Q^{2}}}}$$

FIGURE 12. LOW-PASS OUTPUT

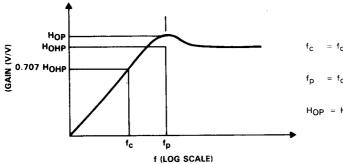

$$f_{c} = f_{o} \times \left[ \sqrt{\left(1 - \frac{1}{2Q^{2}}\right) + \sqrt{\left(1 - \frac{1}{2Q^{2}}\right)^{2} + 1}} \right] - 1$$

$$f_{p} = f_{o} \times \left[ \sqrt{1 - \frac{1}{2Q^{2}}} \right] - 1$$

$$H_{OP} = H_{OHP} \times \frac{1}{\frac{1}{2Q^{2}} \sqrt{1 - \frac{1}{4Q^{2}}}}$$

FIGURE 13. HIGH-PASS OUTPUT