### **General Description**

The HAD8572ARZ family of amplifiers provides input offset voltage correction for very low offset and drift through the use of patented fast step response chopper stabilized techniques.

This method constantly measures and compensates the input offs, eteliminating drift over time and temperature and the effect of 1/f noise. This design breakthrough allows the combination of a gain bandwidth product of 1.5 MHz and a high slew rate of 1.2 V/µs, while only drawing 110µA supply current. These devices are unity gain stable and have good Power Supply Rejection Ratio (PSRR) and Common Mode Rejection Ratio(CMRR).

The HAD8572ARZ series are perfectly suited for applications that require precision amplification of low level signals, in which error sources cannot be tolerated, even in which high bandwidth and fast transition are needed. The rail-to-rail input and output swings make both high-side and low-side sensing easy. The HAD8572ARZ series can operate with a single supply voltage as low as 1.8V for 2-cell battery applications.

The HAD8572ARZ op-amps have enhanced EMI protection to minimize any electromagnetic interference from external sources, and have high electro-static discharge (ESD) protection (5-kV HBM). All models are specified over the extended industrial temperature range of  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ .

### **Features and Benefits**

High DC Precision:

±8 µV (maximum) V<sub>OS</sub> with a Drift of ±40 nV/℃ (maximum)

$A_{VOL}$ : 108 dB (minimum,  $V_{DD}$  = 5.5V) PSRR: 112 dB (minimum,  $V_{DD}$  = 5.5V) CMRR: 112 dB (minimum,  $V_{DD}$  = 5.5V)  $V_{n}$ : 0.45  $\mu V_{PP}$  (typical, f = 0.1 to 10 Hz)

1.5 MHz Bandwidth and 1.2 V/ $\mu$ s Slew Rate Settling Time to 0.1% with 1V Step: 1.2  $\mu$ s Overload Recovery Time to 0.1%: 35  $\mu$ s

110 µA per Amplifier Low Power and 2.0 V to 5.5 V Wide Supply Voltage Range

Operating Temperature Range: -40°C to +125°C

# **Applications**

Precision current sensing

Resistor thermal detectors

Temperature, position and pressure sensors

Medical equipment

Electronic scales

Strain gage amplifiers

Thermocouple amplifiers

Driving A/D Converters

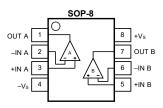

# **Pin Configurations And Pin Description**

| Symbol          | Description                           |

|-----------------|---------------------------------------|

| -IN             | Inverting input of the amplifier.     |

| +IN             | Non-inverting input of the amplifier. |

| +V <sub>S</sub> | Positive (highest) power supply.      |

| -V <sub>S</sub> | Negative (lowest) power supply.       |

| OUT             | Amplifier output.                     |

| NC              | No internal connection.               |

# **Ordering Information**

| Orderable<br>Type Number | Package<br>Name | Package<br>Quantity | Eco Class <sup>(1)</sup> | Operating temperature |  |

|--------------------------|-----------------|---------------------|--------------------------|-----------------------|--|

| HAD8572ARZ               | SOP-8           | 2500                | Green                    | 40°C to +125°C        |  |

**Limiting Value**In accordance with the Absolute Maximum Rating System (IEC 60134).

| Parameter                                          | Absolute Maximum Rating                      |

|----------------------------------------------------|----------------------------------------------|

| Supply Voltage, V <sub>S+</sub> to V <sub>S-</sub> | 10.0 V                                       |

| Signal Input Terminals: Voltage, Current           | $V_{S-}$ – 0.5 V to $V_{S+}$ + 0.5 V, ±20 mA |

| Output Short-Circuit                               | Continuous                                   |

| Storage Temperature Range, T <sub>stg</sub>        | –65 °C to +150 °C                            |

| Junction Temperature, T <sub>J</sub>               | 150 ℃                                        |

| Lead Temperature Range (Soldering 10 sec)          | 260 °C                                       |

# **ESD Rating**

| Parameter Item                     |                                                          | Value  | Unit |

|------------------------------------|----------------------------------------------------------|--------|------|

|                                    | Human body model (HBM), per MIL-STD-883J / Method 3015.9 |        |      |

| Electrostatic<br>Discharge Voltage | Charged device model (CDM), per ESDA/JEDEC JS-002-2014   | ±2 000 | V    |

|                                    | Machine model (MM), per JESD22-A115C                     | ±250   |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Electrical Characteristics**

$V_S$  = 5.0V,  $T_A$  = +25°C,  $V_{CM}$  =  $V_S/2$ ,  $V_O$  =  $V_S/2$ , and  $R_L$  = 10k $\Omega$  connected to  $V_S/2$ , unless otherwise noted. Boldface limits apply over the specified temperature range,  $T_A$  = -40 to +125 °C.

| Symbol             | Parameter                   | Conditions                                                                          | Min.               | Тур. | Max.                 | Unit              |

|--------------------|-----------------------------|-------------------------------------------------------------------------------------|--------------------|------|----------------------|-------------------|

| OFFSET             | VOLTAGE                     |                                                                                     |                    |      |                      |                   |

| V <sub>os</sub>    | Input offset voltage        |                                                                                     |                    | ±0.5 | ±8                   | μV                |

| V <sub>os</sub> TC | Offset voltage drift        | T <sub>A</sub> = −40 to +125 °C                                                     |                    | ±5   | ±40                  | nV/℃              |

| PSRR               | Power supply rejection      | $V_S = 2.0 \text{ to } 5.5 \text{ V}, V_{CM} < V_{S+} - 2 \text{V}$                 | 112                | 126  |                      | dB                |

| FORK               | ratio                       | T <sub>A</sub> = −40 to +125 °C                                                     | 106                |      |                      | UB                |

| INPUT BI           | AS CURRENT                  |                                                                                     |                    |      |                      |                   |

|                    |                             |                                                                                     |                    | 70   |                      |                   |

| I <sub>B</sub>     | Input bias current          | T <sub>A</sub> = 0 to +85 ℃                                                         |                    |      | 370                  | pА                |

|                    |                             | T <sub>A</sub> = −40 to +125 °C                                                     |                    |      | 800                  |                   |

|                    |                             |                                                                                     |                    | 100  |                      |                   |

| I <sub>os</sub>    | Input offset current        | T <sub>A</sub> = 0 to +85 ℃                                                         |                    |      | 800                  | pА                |

|                    |                             | T <sub>A</sub> = −40 to +125 °C                                                     | ]                  |      | 1,000                |                   |

| NOISE              |                             |                                                                                     |                    |      |                      |                   |

| \/                 | Input voltage noise         | f=0.01 to 1 Hz                                                                      |                    | 0.1  |                      | μV <sub>P-P</sub> |

| V <sub>n</sub> In  | input voitage noise         | f=0.1 to 10 Hz                                                                      |                    | 0.45 |                      | μν <sub>Ρ-Ρ</sub> |

| 0                  | Input voltage noise         | f = 10 kHz                                                                          |                    | 27   |                      | nV/√Hz            |

| e <sub>n</sub>     | density                     | f = 1 kHz                                                                           |                    | 30   |                      | IIV/ VIIZ         |

| In                 | Input current noise density | f = 1 kHz                                                                           |                    | 10   |                      | fA/√Hz            |

| INPUT VO           | DLTAGE                      |                                                                                     |                    |      |                      |                   |

| V <sub>CM</sub>    | Common-mode voltage range   |                                                                                     | V <sub>S</sub> 0.1 |      | V <sub>S+</sub> +0.1 | V                 |

|                    |                             | $V_S = 5.5 \text{ V}, V_{CM} = -0.1 \text{ to } 5.5 \text{ V}$                      | 112                | 130  |                      |                   |

| CMRR               | Common-mode rejection ratio | $V_{CM} = 0 \text{ to } 5.3 \text{ V}, T_A = -40 \text{ to } +125 ^{\circ}\text{C}$ | 106                |      | 7                    | dB                |

| CIVILLE            |                             | $V_S = 2.0 \text{ V}, V_{CM} = -0.1 \text{ to } 2.0 \text{ V}$                      | 102                | 122  |                      | l db              |

|                    |                             | $V_{CM} = 0 \text{ to } 1.8 \text{ V}, T_A = -40 \text{ to } +125 ^{\circ}\text{C}$ | 96                 |      |                      |                   |

| INPUT IM           | PEDANCE                     |                                                                                     |                    |      |                      |                   |

| R <sub>IN</sub>    | Input resistance            |                                                                                     | 100                |      |                      | GΩ                |

| C <sub>IN</sub>    | Input capacitance           | Differential                                                                        |                    | 2.0  |                      | pF                |

| O <sub>IN</sub>    | піриї сарасітапсе           | Common mode                                                                         |                    | 3.5  |                      | Pi                |

| OPEN-LC            | OP GAIN                     |                                                                                     |                    |      |                      |                   |

|                    |                             | $R_L = 10 \text{ k}\Omega$ , $V_O = 0.05 \text{ to } 3.5 \text{ V}$                 | 108                | 128  |                      |                   |

| A <sub>VOL</sub>   | Open-loop voltage gain      | $T_A = -40 \text{ to } +125 ^{\circ}\text{C}$                                       | 102                |      |                      | dB                |

|                    | Open-loop voltage gain      | $R_L = 600 \Omega$ , $V_O = 0.15 \text{ to } 3.5 \text{ V}$                         | 96                 | 116  |                      | L GB              |

|                    |                             | T <sub>A</sub> = −40 to +125 °C                                                     | 90                 |      |                      |                   |

| FREQUE             | NCY RESPONSE                |                                                                                     |                    |      |                      |                   |

| GBW                | Gain bandwidth product      | f = 1 kHz                                                                           |                    | 1.5  |                      | MHz               |

| SR                 | Slew rate                   | $G = +1$ , $C_L = 100 \text{ pF}$ , $V_O = 1.5 \text{ to } 3.5 \text{ V}$           |                    | 1.2  |                      | V/µs              |

| Symbol                | Parameter                         | Conditions                                       | Min. | Тур.                | Max.                | Unit |  |

|-----------------------|-----------------------------------|--------------------------------------------------|------|---------------------|---------------------|------|--|

|                       | 0 - 441: 4:                       | To 0.1%, G = +1, 1V step                         |      | 1.2                 |                     |      |  |

| t <sub>s</sub>        | Settling time                     | To 0.01%, G = +1, 1V step                        |      | 1.5                 |                     | μs   |  |

| t <sub>or</sub>       | Overload recovery time            | To 0.1%, V <sub>IN</sub> * Gain > V <sub>S</sub> |      | 35                  |                     | μs   |  |

| OUTPUT                | •                                 |                                                  |      |                     |                     |      |  |

| ./                    | High output voltage swing         | $R_L = 10 \text{ k}\Omega$                       |      | V <sub>S+</sub> -12 | V <sub>S+</sub> -15 | mV   |  |

| V <sub>OH</sub>       | TilgiToutput voltage swilig       | I <sub>LOAD</sub> = 1 mA, source current         |      | V <sub>S+</sub> –50 | V <sub>S+</sub> -60 | 1117 |  |

| $V_{OL}$              | Low output voltage swing          | $R_L = 10 \text{ k}\Omega$                       |      | 9                   | 12                  | mV   |  |

| <b>V</b> OL           | Low output voltage swing          | I <sub>LOAD</sub> = 1 mA, sink current           |      | 32                  | 40                  | inv  |  |

| Z <sub>OUT</sub>      | Open-loop output impedance        | f = 350 kHz, I <sub>O</sub> = 0                  |      | 2                   |                     | kΩ   |  |

| ı                     | Short-circuit current             | Source current through 10Ω                       |      | 40                  |                     | A    |  |

| SC                    | Snort-circuit current             | Sink current through $10\Omega$                  |      | 50                  |                     | mA   |  |

| POWER S               | SUPPLY                            |                                                  |      |                     |                     |      |  |

| V <sub>s</sub>        | Operating supply voltage          | T <sub>A</sub> = 0 to +70 °C                     | 1.8  |                     | 6.0                 | V    |  |

| <b>v</b> <sub>S</sub> | Operating supply voltage          | $T_A = -40 \text{ to } +125 ^{\circ}\text{C}$    | 2.0  |                     | 6.0                 | \ \  |  |

| lα                    | Quiescent current (per amplifier) |                                                  | 80   | 110                 | 140                 | μA   |  |

| THERMAL               | L CHARACTERISTICS                 |                                                  |      |                     |                     |      |  |

| T <sub>A</sub>        | Operating temperature range       |                                                  | -40  |                     | +125                | ℃    |  |

|                       | Package Thermal<br>Resistance     | SOP-8                                            |      | 125                 |                     | °C/W |  |

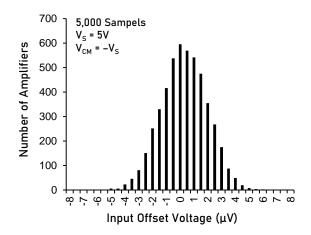

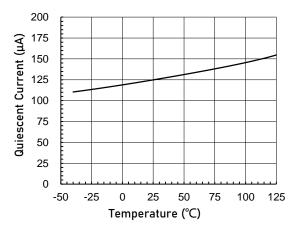

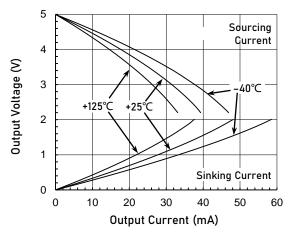

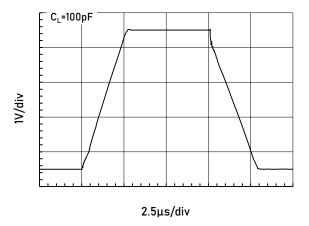

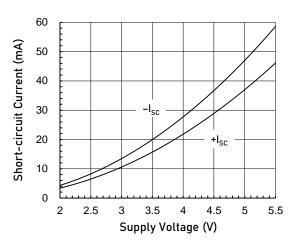

### **Typical Performance Characteristics**

At  $T_A$ =+25°C,  $V_S$ =±2.5V,  $V_{CM}$ = $V_S$ /2,  $R_L$ =10k $\Omega$  connected to  $V_S$ /2, and  $C_L$ =100pF, unless otherwise noted.

Input Offset Voltage Production Distribution.

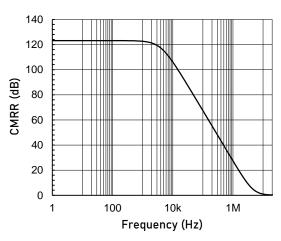

Common-mode Rejection Ratio as a function of Frequency.

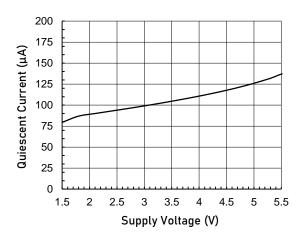

Quiescent Current as a function of Supply Voltage.

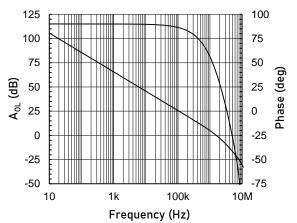

Open-loop Gain and Phase as a function of Frequency.

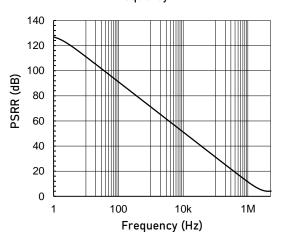

Power Supply Rejection Ratio as a function of Frequency.

Quiescent Current as a function of Temperature.

Output Voltage Swing as a function of Output Current.

Large Signal Step Response (4V Step).

Short-circuit Current as a function of Supply Voltage.

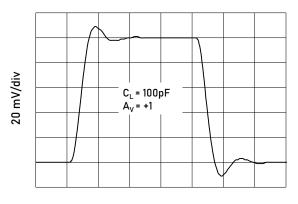

0.25 μs/div

Small Signal Step Response (100mV Step).

### **Application Notes**

The HAD8572ARZ operational amplifiers are unity-gain stable and free from unexpected output phase reversal. These devices use a proprietary auto-calibration technique to provide low offset voltage and very low drift over time and temperature. For lowest offset voltage and precision performance, optimize circuit layout and mechanical conditions. Avoid temperature gradients that create thermoelectric (Seebeck) effects in the thermocouple junctions formed from connecting dissimilar conductors. Cancel these thermally-generated potentials by assuring they are equal on both input terminals. Other layout and design considerations include:

- Use low thermoelectric-coefficient conditions (avoid dissimilar metals).

- Thermally isolate components from power supplies or other heat sources.

- Shield operational amplifier and input circuitry from air currents, such as cooling fans.

Following these guidelines reduces the likelihood of junctions being at different temperatures, which can cause thermoelectric voltages of  $0.1\mu V/^{\circ}C$  or higher, depending on materials used.

#### **OPERATING VOLTAGE**

The HAD8572ARZ family is fully specified and ensured for operation from 2.0V to 5.5V ( $\pm 1.0$ V to  $\pm 2.75$ V). In addition, many specifications apply from -40°C to +125°C.

Parameters that vary significantly with operating voltages or temperature are illustrated in the Typical Characteristics graphs.

NOTE: Supply voltages ( $V_{S+}$  to  $V_{S-}$ ) higher than +10V can permanently damage the device.

#### INPUT VOLTAGE

The input common-mode voltage range of the HAD8572ARZ series extends 100mV beyond the negative supply rail and reaches the positive supply rail. This performance is achieved with a complementary input stage: an N-channel input differential pair in parallel with a P-channel differential pair. The N-channel pairis active for input voltages close to the positive rail, typically Vs+-1.4V to the positive supply, whereas the P-channel pair is active for inputs from 200mV below the negative supply to approximately Vs+-1.4V. There is a small transition region, typically Vs+-1.2V to Vs+-1V, in which both pairs are on. This 200mV transition region can vary up to 200mV with process variation. Thus, the transition region (both stages on) can range from Vs+-1.4V to Vs+-1.2V on the low end, up to Vs+-1V to Vs+-0.8V on the high end. Within this transition region, PSRR, CMRR, offset voltage, offset drift, and THD can be degraded compared to device operation outside this region.

The typical input bias current of the HAD8572ARZ

during normal operation is approximately 70pA. In driven conditions, the bias current can increase significantly. The most common cause of an overdriven condition occurs when the operational amplifier is outside of the linear range of operation. When the output of the operational amplifier is driven to one of the supply rails, the feedback loop requirements cannot be satisfied and a differential input voltage develops across the input pins. This differential input voltage results in activation of parasitic diodes inside the front-end input chopping

switches that combine with electromagnetic interference (EMI) filter resistors to create the equivalent circuit. Notice that the input bias current remains within specification in the linear region.

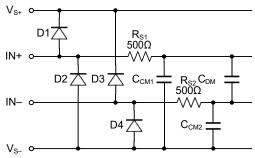

#### INPUT EMI FILTER AND CLAMP CIRCUIT

Figure 1 shows the input EMI filter and clamp circuit. The HAD8572ARZ op-amps have internal ESD protection diodes (D1, D2, D3, and D4) that are connected between the inputs and each supply rail. These diodes protect the input transistors in the event of electrostatic discharge and are reverse biased during normal operation. This protection scheme allows voltages as high as approximately 500mV beyond the rails to be applied at the input of either terminal without causing permanent damage. See the table of Absolute Maximum Ratings for more information.

Operational amplifiers vary in susceptibility to EMI. If conducted EMI enters the operational amplifier, the dc offset at the amplifier output can shift from its nominal value when EMI is present. This shift is a result of signal rectification associated with the internal semiconductor junctions. Although all operational amplifier pin functions can be affected by EMI, the input pins are likely to be the most susceptible. The EMI filter of the HAD8572ARZ family is composed of two 5-k $\Omega$  input series resistors (Rs1 and Rs2), two common-mode capacitors (CcM1 and CcM2), and a differential capacitor (CDM). These RC networks set the -3dB

low-pass cutoff frequencies at 35-MHz for common-mode signals, and at 22-MHz for differential signals.

Figure 1. Input EMI Filter and Clamp Circuit

### **Application Notes**

#### INTERNAL OFFSET CORRECTION

The HAD8572ARZ operational amplifiers use an autocalibration technique with a time-continuous 500kHz operational amplifier in the signal path. This amplifier is zero-corrected every 2 $\mu$ s using a proprietary technique. Upon power up, the amplifier requires approximately 100 $\mu$ s to achieve specified  $V_{OS}$  accuracy. This design has no aliasing or flicker noise.

#### CAPACITIVE LOAD AND STABILITY

The HAD8572ARZ family can safely drive capacitive loadsof up to 500pF in any configuration. As with mostamplifiers, driving larger capacitive loads than specified may cause excessive overshoot and ringing, or even oscillation. A heavy capacitive load reduces the phase margin and causes the amplifier frequency response to peak. Peaking corresponds to overshooting or ringing in the time domain. Therefore, it is recommended that external compensation be used if the HAD8572ARZ op-amps must drive a load exceeding 500pF.

This compensation is particularly important in the unity-gain configuration, which is the worst case for stability.

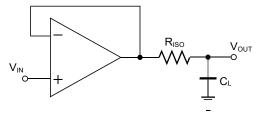

A quick and easy way to stabilize the op-amp for capacitive load drive is by adding a series resistor,  $R_{\rm ISO}$ , between the amplifier output terminal and the load capacitance, as shown in Figure 2.  $R_{\rm ISO}$  isolates the amplifier output and feedback network from the capacitive load. The bigger the  $R_{\rm ISO}$  resistor value, the more stable  $V_{\rm OUT}$  will be. Note that this method results in a loss of gain accuracy because  $R_{\rm ISO}$  forms a voltage divider with the  $R_{\rm L}$ .

Figure 2. Indirectly Driving Heavy Capacitive Load

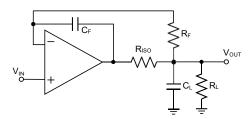

An improvement circuit is shown in Figure 3. It provides DC accuracy as well as AC stability. The  $R_{\text{F}}$  provides the DC accuracy by connecting the inverting signal with the output.

The  $C_F$  and  $R_{\rm ISO}$  serve to counteract the loss of phase margin by feeding the high frequency component of the output signal back to the amplifier's inverting input, thereby preserving phase margin in the overall feedback loop.

For no-buffer configuration, there are two others ways to increase the phase margin: (a) by increasing the amplifier's gain, or (b) by placing a capacitor in

parallel with the feedback resistor to counteract the parasitic capacitance associated with inverting node.

Figure 3. Indirectly Driving Heavy Capacitive Load with DC Accuracy

#### OVERLOAD RECOVERY

Overload recovery is defined as the time required for the operational amplifier output to recover from a saturated state to a linear state. The output devices of the operational amplifier enter a saturation region when the output voltage exceeds the rated operating voltage, either because of the high input voltage or the high gain. After the device enters the saturation region, the charge carriers in the output devices require time to return back to the linear state. After the charge carriers return back to the linear state, the device begins to slew at the specified slew rate. Thus, the propagation delay in case of an overload condition is the sum of the overload recovery time and the slew time. The overload recovery time for the HAD8572ARZ family is approximately 35µs.

### EMI REJECTION RATIO

Circuit performance is often adversely affected by high frequency EMI. When the signal strength is low and transmission lines are long, an op-amp must accurately amplify the input signals. However, all opamp pins — the non-inverting input, inverting input, positive supply, negative supply, and output pins — are susceptible to EMI signals. These high frequency signals are coupled into an op-amp by various means, such as conduction, near field radiation, or far field radiation. For example, wires and printed circuit board (PCB) traces can act as antennas and pick up high frequency EMI signals.

Amplifiers do not amplify EMI or RF signals due to their relatively low bandwidth. However, due to the nonlinearities of the input devices, op-amps can rectify these out of band signals. When these high frequency signals are rectified, they appear as a dc offset at the output.

The HAD8572ARZ op-amps have integrated EMI filters at their input stage. A mathematical method of measuring EMIRR is defined as follows:

EMIRR = 20 log  $(V_{IN PEAK}/\Delta V_{OS})$

### **Application Notes**

MÄXIMIZING PERFORMANCE THROUGH PROPER LAYOUT

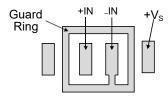

To achieve the maximum performance of the extremely high input impedance and low offset voltage of the HAD8572ARZ op-amps, care is needed in laying out the circuit board. The PCB surface must remain clean and free of moisture to avoid leakage currents between adjacent traces. Surface coating of the circuit board reduces surface moisture and provides a humidity barrier, reducing parasitic resistance on the board. The use of guard rings around the amplifier inputs further reduces leakage currents. Figure 4 shows proper guard ringconfiguration and the top view of a surface -mount layout The guard ring does not need to be a specific width, but it should form a continuous loop around both inputs. By setting the guard ring voltage equal to the voltage at the non-inverting input, parasitic capacitance is minimized as well. For further reduction of leakage currents, components can be mounted to the PCB using Teflon standoff insulators.

Figure 4. Use a guard ring around sensitive pins

Other potential sources of offset error are thermoelectric voltages on the circuit board. This voltage, also called Seebeck voltage, occurs at the junction of two dissimilar metals and is proportional to the temperature of the junction. The most common metallic junctions on a circuit board are solder-to-board trace and solder-to-component lead. If the temperature of the PCB at one end of the component is different from the temperature at the other end, the resulting Seebeck voltages are not equal, resulting in a thermal voltage error.

This thermocouple error can be reduced by using dummy components to match the thermoelectric error source. Placing the dummy component as close as possible to its partner ensures both Seebeck voltages are equal, thus canceling the thermocouple error. Maintaining a constant ambient temperature on the circuit board further reduces this error. The use of a ground plane helps distribute heat throughout the board and reduces EMI noise pickup.

#### INPUT-TO-OUTPUT COUPLING

To minimize capacitive coupling, the input and output signal traces should not be parallel. This helps reduce unwanted positive feedback.

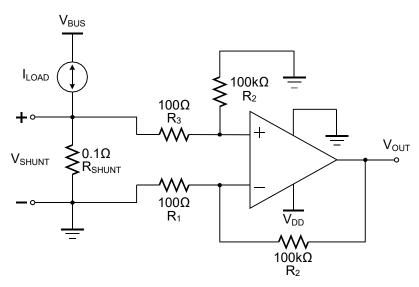

#### PRECISION LOW-SIDE CURRENT SHUNT SENSING

Many applications require the sensing of signals near the positive or negative rails. Current shunt sensing is one such application and is mostly used for feedback control systems. It is also used in a variety of other applications, including power metering, battery fuel gauging, and feedback controls in industrial applications. In such applications, it is desirable to use a shunt with very low resistance to minimize series voltage drop. This configuration not only minimizes wasted power, but also allows the measurement of high currents while saving power.

A typical shunt may be  $100m\Omega$ . At a measured current of 1A, the voltage produced from the shunt is 100mV, and the amplifier error sources are not critical. However, at low measured current in the 1mA range, the  $100\mu V$  generated across the shunt demands a very low offset voltage and drift amplifier to maintain absolute accuracy.

The unique attributes of a zero drift amplifier provide a solution. Figure 5 shows a low-side current sensing circuit using the HAD8572ARZ . The HAD8572ARZ are configured as difference amplifiers with a gain of 1000. Although the HAD8572ARZ have high CMRR, the CMRR of the system is limited by the external resistors. Therefore, the key to high CMRR for the system is resistors that are well matched from both the resistive ratio and relative drift, where  $R_1/R_2 = R_3/R_4$ . The transfer function is given by:

$$V_{OUT} = V_{SHUNT} \times Gain_{Diff\_Amp} = (R_{SHUNT} \times I_{LOAD}) \times (R_2 / R_1) = 100 \times I_{LOAD}$$

Figure 5. Low-Side Current Sensing Circuit

Any unused channel of the HAD8572ARZ must be configured in unity gain with the input common-mode voltage tied to the midpoint of the power supplies.

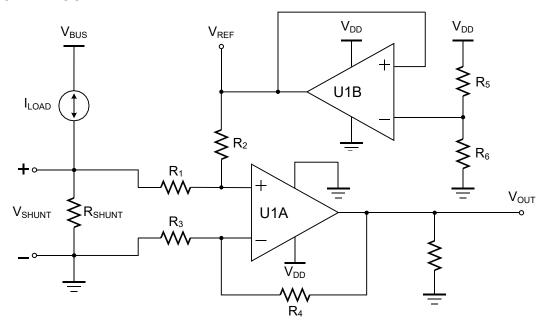

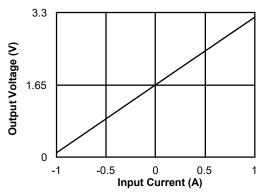

#### BIDIRECTIONAL CURRENT-SENSING

This single-supply, low-side, bidirectional current-sensing solution detects load currents from –1A to +1A. The single-ended output spans from 110mV to 3.19V. This design uses the HAD8572ARZ because of its low offset voltage and rail-to-rail input and output. One of the amplifiers is configured as a difference amplifier and the other amplifier provides the reference voltage.

Figure 6 shows the solution. This solution has the following requirements:

- Supply voltage: 3.3V

- Input: -1A to +1A

- Output: 1.65V±1.54V (110mV to 3.19V)

There are two types of errors in this design: offset and gain. Gain errors are introduced by the tolerance of the shunt resistor and the ratios of  $R_4$  to  $R_3$  and, similarly,  $R_2$  to  $R_1$ . Offset errors are introduced by the voltage divider ( $R_5$  and  $R_6$ ) and how closely the ratio of  $R_4/R_3$  matches  $R_2/R_1$ . The latter value affects the CMRR of the difference amplifier, ultimately translating to an offset error.

Figure 6. Bidirectional Current-Sensing Schematic

The load current,  $I_{LOAD}$ , flows through the shunt resistor ( $R_{SHUNT}$ ) to develop the shunt voltage,  $V_{SHUNT}$ . The shunt voltage is then amplified by the difference amplifier consisting of U1A and  $R_1$  through  $R_4$ . The gain of the difference amplifier is set by the ratio of  $R_4$  to  $R_3$ . To minimize errors, set  $R_2 = R_4$  and  $R_1 = R_3$ . The reference voltage,  $V_{REF}$ , is supplied by buffering a resistor divider using U1B. The transfer function is given by Equation 1.

$$V_{OUT} = V_{SHUNT} \times Gain_{Diff\_Amp} + V_{REF}$$

Where

- V<sub>SHUNT</sub> = I<sub>LOAD</sub> × R<sub>SHUNT</sub>

- Gain<sub>Diff Amp</sub> =  $R_4/R_3$

•

$$V_{REF} = V_{DD} \times [R_6 / (R_5 + R_6)]$$

(1)

There are two types of errors in this design: offset and gain. Gain errors are introduced by the tolerance of the shunt resistor and the ratios of  $R_4$  to  $R_3$  and, similarly,  $R_2$  to  $R_1$ . Offset errors are introduced by the voltage divider ( $R_5$  and  $R_6$ ) and how closely the ratio of  $R_4/R_3$  matches  $R_2/R_1$ . The latter value affects the CMRR of the difference amplifier, ultimately translating to an offset error.

The value of  $V_{SHUNT}$  is the ground potential for the system load because  $V_{SHUNT}$  is a low-side measurement. Therefore, a maximum value must be placed on  $V_{SHUNT}$ . In this design, the maximum value for  $V_{SHUNT}$  is set to 100mV. Equation 2 calculates the maximum value of the shunt resistor given a maximum shunt voltage of 100mV and maximum load current of 1A.

$$R_{SHUNT(MAX)} = V_{SHUNT(MAX)} / I_{LOAD(MAX)} = 100 \text{mV} / 1 \text{A} = 100 \text{ m} - \Omega$$

(2)

The tolerance of R<sub>SHUNT</sub> is directly proportional to cost. For this design, a shunt resistor with a tolerance of 0.5% was selected. If greater accuracy is required, select a 0.1% resistor or better.

The load current is bidirectional; therefore, the shunt voltage range is -100 mV to +100 mV. This voltage is divided down by  $R_1$  and  $R_2$  before reaching the operational amplifier, U1A. Take care to ensure that the voltage present at the non-inverting node of U1A is within the common-mode range of the device. Therefore, use an operational amplifier, such as the HAD8572ARZ, that has a common-mode range that extends below the negative supply voltage. Finally, to minimize offset error, note that the AD857ARZ has a typical offset voltage of merely  $\pm 0.5 \mu \text{V}$  ( $\pm 8 \mu \text{V}$  maximum).

Given a symmetric load current of –1A to +1A, the voltage divider resistors ( $R_5$  and  $R_6$ ) must be equal. To be consistent with the shunt resistor, a tolerance of 0.5% was selected. To minimize power consumption,  $10k\Omega$  resistors were used.

To set the gain of the difference amplifier, the common-mode range and output swing of the AD857ARZ must beconsidered. Equation 3 and Equation 4 depict the typical common-mode range and maximum output swing, respectively, of the HAD8572ARZ given a 3.3V supply.

•

$$-100 \text{mV} < V_{\text{CM}} < 3.4 \text{V}$$

(3)

•

$$100\text{mV} < V_{\text{OUT}} < 3.2\text{V}$$

(4)

The gain of the difference amplifier can now be calculated as shown in Equation 5.

Gain<sub>Diff\_Amp</sub> =

$$(V_{OUT_MAX} - V_{OUT_MIN}) / [R_{SHUNT} \times (I_{MAX} - I_{MIN})]$$

=  $(3.2V - 100 \text{mV}) / 100 \text{m}\Omega \times [1A - (-1A)] = 15.5 \text{ V/V}$  (5)

The resistor value selected for  $R_1$  and  $R_3$  was  $1k\Omega$ .  $15.4k\Omega$  was selected for  $R_2$  and  $R_4$  because this number is the nearest standard value. Therefore, the ideal gain of the difference amplifier is 15.4V/V.

The gain error of the circuit primarily depends on  $R_1$  through  $R_4$ . As a result of this dependence, 0.1% resistors were selected. This configuration reduces the likelihood that the design requires a two-point calibration. A simple one-point calibration, if desired, removes the offset errors introduced by the 0.5% resistors.

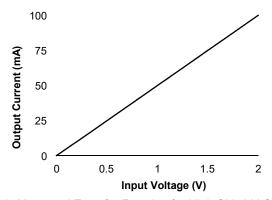

Figure 7. Bidirectional Current-Sensing Circuit Performance: Output Voltage vs. Input Current

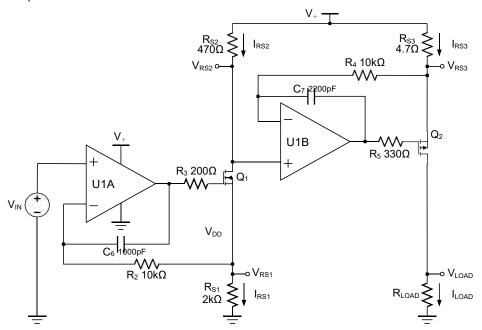

#### HIGH-SIDE VOLTAGE-TO-CURRENT (V-I) CONVERTER

The circuit shown in Figure 8 is a high-side voltage-to-current (V-I) converter. It translates in input voltage of 0V to 2V to and output current of 0mA to 100mA.

Figure 8. Bidirectional Current-Sensing Schematic

The design requirements are as follows:

Supply Voltage: 5V DC

Input: 0V to 2V DC

Output: 0mA to 100mA DC

The V-I transfer function of the circuit is based on the relationship between the input voltage,  $V_{IN}$ , and the three current sensing resistors,  $R_{S1}$ ,  $R_{S2}$ , and  $R_{S3}$ . The relationship between  $V_{IN}$  and  $R_{S1}$  determines the current that flows through the first stage of the design. The current gain from the first stage to the second stage is based on the relationship between  $R_{S2}$  and  $R_{S3}$ .

For a successful design, pay close attention to the dc characteristics of the operational amplifier chosen for the application. To meet the performance goals, this application benefits from an operational amplifier with low offset voltage, low temperature drift, and rail-to-rail output. The HAD8572ARZ CMOS operational amplifier is a high-precision, typically  $0.5\mu V$  offset,  $5nV/^{\circ}C$  drift amplifier optimized for low-voltage, single-supply operation with an output swing to within 15mV (at  $R_L=10k\Omega$ ) of the positive rail. The HAD8572ARZ family uses chopping techniques to provide low initial offset voltage and near-zero drift over time and temperature. Low offset voltage and low drift reduce the offset error in the system, making these devices appropriate for precise dc control. The rail-to-rail output stage of the HAD8572ARZ ensures that the output swing of the operational amplifier is able to fully control the gate of the MOSFET devices within the supply rails.

Figure 9 shows the measured transfer function for this circuit. The low offset voltage and offset drift of the 2 facilitate excellent dc accuracy for the circuit.

Figure 9. Measured Transfer Function for High-Side V-I Converter

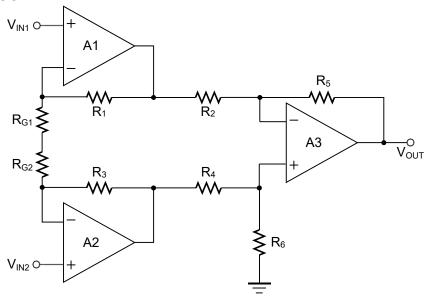

#### SINGLE-SUPPLY INSTRUMENTATION AMPLIFIER

The extremely low offset voltage and drift, high open-loop gain, high common-mode rejection, and high power supply rejection of the HAD8572ARZ make them excellent op-amp choices as discrete, single-supply instrumentation amplifiers.

Figure 10 shows the classic 3-op-amp instrumentation amplifier using the HAD8572ARZ. The key to high CMRR for the instrumentation amplifier are resistors that are well matched for both the resistive ratio and relative drift. For true difference amplification, matching of the resistor ratio is very important, where:

R<sub>5</sub>/R<sub>2</sub> = R<sub>6</sub>/R<sub>4</sub>

•  $R_{G1} = R_{G2}$ ,  $R_1 = R_3$ ,  $R_2 = R_4$ ,  $R_5 = R_6$

•  $V_{OUT} = (V_{IN1} - V_{IN2}) \times (1 + R_1/R_{G1}) \times (R_5/R_2)$

The resistors are important in determining the performance over manufacturing tolerances, time, and temperature. Assuming a perfect unity-gain difference amplifier with infinite common-mode rejection, a 1% tolerance resistor matching results in only 34dB of common-mode rejection. Therefore, at least 0.01% or better resistors are recommended.

To build a discrete instrumentation amplifier with external resistors without compromising on noise, pay close attention to the resistor values chosen.  $R_{G1}$  and  $R_{G2}$  each have thermal noise that is amplified by the total noise gain of the instrumentation amplifier and, therefore, a sufficiently low value must be chosen to reduce thermal noise contribution at the output while still providing an accurate measurement.

Figure 10. Discrete 3-Op-amp Instrumentation Amplifier

Figure 11 shows the external resistors noise contribution referred to the output.

| Resistor        | Value  | Resistor Thermal Noise | Thermal Noise Referred to Output |

|-----------------|--------|------------------------|----------------------------------|

| R <sub>G1</sub> | 0.4 kΩ | 2.57 nV/√Hz            | 128.30 nV/√Hz                    |

| R <sub>G2</sub> | 0.4 kΩ | 2.57 nV/√Hz            | 128.30 nV/√Hz                    |

| $R_1$           | 10 kΩ  | 12.83 nV/√Hz           | 25.66 nV/√Hz                     |

| $R_2$           | 10 kΩ  | 12.83 nV/√Hz           | 25.66 nV/√Hz                     |

| $R_3$           | 10 kΩ  | 12.83 nV/√Hz           | 25.66 nV/√Hz                     |

| $R_4$           | 10 kΩ  | 12.83 nV/√Hz           | 25.66 nV/√Hz                     |

| R <sub>5</sub>  | 20 kΩ  | 18.14 nV/√Hz           | 18.14 nV/√Hz                     |

| R <sub>6</sub>  | 20 kΩ  | 18.14 nV/√Hz           | 18.14 nV/√Hz                     |

Figure 11. Thermal Noise Contribution Example

Note that A1 and A2 have a high gain of  $1 + R_1/R_{G1}$ . Therefore, use a high precision, low offset voltage and low noise amplifier for A1 and A2, such as the HAD8572ARZ. Conversely, A3 operates at a much lower gain and has a different set of op-amp requirements. Its input noise, referred to the overall instrumentation amplifier input, is divided by the first stage gain and is not as important. Note that the input offset voltage and the input voltage noise of the amplifiers are also amplified by the overall noise gain.

Any unused channel of the HAD8572ARZ must be configured in unity gain with the input common-mode voltage tied to the midpoint of the power supplies.

Understanding how noise impacts a discrete instrumentation amplifier or a difference amplifier (the second stage of a 3-op-amp instrumentation amplifier) is important, because they are commonly used in many different applications.

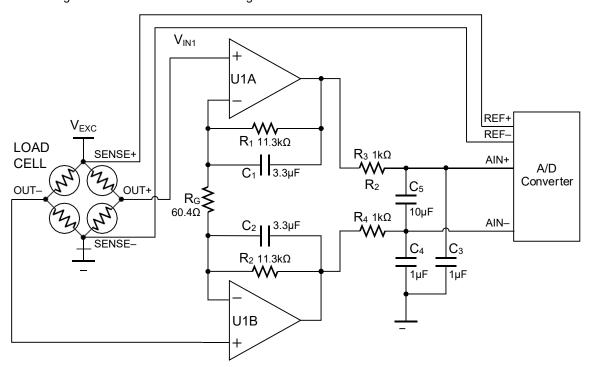

### LOAD CELL (STRAIN GAGE) SENSOR SIGNAL CONDITIONING

The HAD8572ARZ, with its ultralow offset, drift, and noise, is well suited to signal condition a low level sensor output with high gain and accuracy. A weigh scale (load cell) is an example of an application with such requirements. Figure 12 shows a configuration for a single-supply, precision, weigh scale measurement system. The HAD8572ARZ is used at the front end for amplification of the low level signal from the load cell.

Current flowing through a PCB trace produces an IR voltage drop; with longer traces, this voltage drop can be several millivolts or more, introducing a considerable error. A 1 inch long, 0.005 inch wide trace of 1 oz copper has a resistance of approximately  $100m\Omega$  at room temperature. With a load current of 10mA, the resistance can introduce a 1mV error.

Therefore, a 6-wire load cell is used in the circuit. The load cell has two sense pins, in addition to excitation, ground, and two output connections. The sense pins are connected to the high side (excitation pin) and low side (ground pin) of the Wheatstone bridge. The voltage across the bridge can then be accurately measured regardless of voltage drop due to wire resistance. The two sense pins are also connected to the analog-to-digital converter (ADC) reference inputs for a ratio-metric configuration that is immune to low frequency changes in the power supply excitation voltage.

The HAD8572ARZ is configured as the first stage of a 3-op-amp instrumentation amplifier to amplify the low level amplitude signal from the load cell by a factor of 1 +  $2R_1/R_G$ . Capacitors  $C_1$  and  $C_2$  are placed in the feedback loops of the amplifiers and interact with  $R_1$  and  $R_2$  to perform low-pass filtering. This filtering limits the amount of noise entering the  $\Sigma$ - $\Delta$  ADC. In addition,  $C_3$ ,  $C_4$ ,  $C_5$ ,  $R_3$  and  $R_4$  provide further common-mode and differential mode filtering to reduce noise and unwanted signals.

Figure 12. Precision Weigh Scale Measurement System

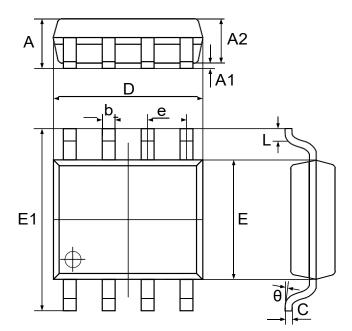

# **Package Outlines (continued)**

**DIMENSIONS, SOP-8**

| Symbol |            | nsions<br>meters | Dimensions<br>In Inches |        |  |

|--------|------------|------------------|-------------------------|--------|--|

|        | Min        | Max              | Min Max                 |        |  |

| Α      | 1.370      | 1.670            | 0.054                   | 0.066  |  |

| A1     | 0.070      | 0.170            | 0.003                   | 0.007  |  |

| A2     | 1.300      | 1.500            | 0.051                   | 0.059  |  |

| b      | 0.306      | 0.506            | 0.012                   | 0.020  |  |

| С      | 0.203      | 0.203 TYP. 0.00  |                         | 3 TYP. |  |

| D      | 4.700      | 5.100            | 0.185                   | 0.201  |  |

| Е      | 3.820      | 4.020            | 0.150                   | 0.158  |  |

| E1     | 5.800      | 6.200            | 0.228                   | 0.244  |  |

| е      | 1.270 TYP. |                  | 0.050                   | TYP.   |  |

| L      | 0.450      | 0.750            | 0.018                   | 0.030  |  |

| θ      | 0°         | 8°               | 0° 8°                   |        |  |

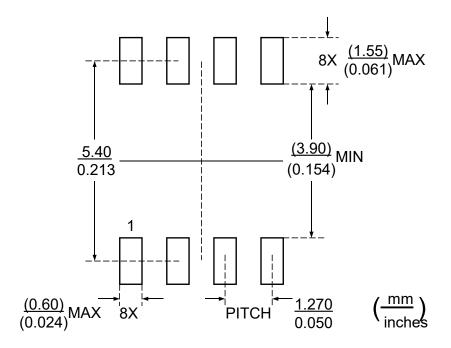

RECOMMENDED SOLDERING FOOTPRINT, SO-8

### **Attention**

- Any and all HUA XUAN YANG ELECTRONICS products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your HUA XUAN YANG ELECTRONICS representative nearest you before using any HUA XUAN YANG ELECTRONICS products described or contained herein in such applications.

- HUA XUAN YANG ELECTRONICS assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all HUA XUAN YANG ELECTRONICS products described or contained herein.

- Specifications of any and all HUA XUAN YANG ELECTRONICS products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- HUA XUAN YANG ELECTRONICS CO.,LTD. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all HUA XUAN YANG ELECTRONICS products(including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of HUA XUAN YANG ELECTRONICS CO.,LTD.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

HUA XUAN YANG ELECTRONICS believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc.

When designing equipment, refer to the "Delivery Specification" for the HUA XUAN YANG ELECTRONICS product that you intend to use.