# **BGW200EG**

# IEEE 802.11b System-in-Package Rev. 01 — 18 July 2007

**Product data sheet**

#### 1. **General description**

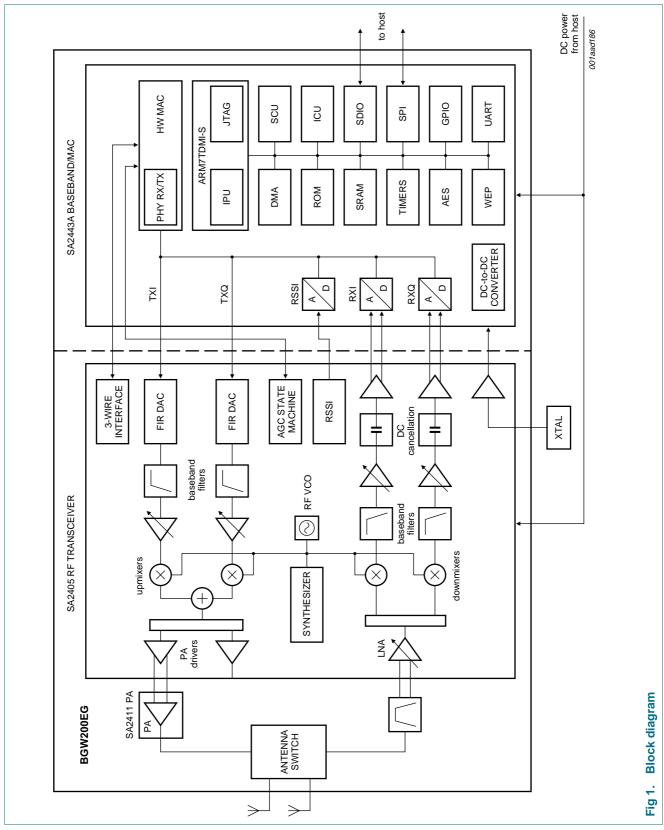

The BGW200EG is a plug-and-play System-in-Package (SiP) for IEEE Std 802.11b - 1999 Wireless Local Area Network (WLAN) intended for embedded and mobile applications.

The BGW200EG comprises an ARM7TDMI microcontroller with SRAM and ROM, an 802.11b Medium Access Controller (MAC) and compliant modem, a highly integrated RF transceiver, a linear power amplifier and an RF front-end with integrated baluns, filters and switches.

The power management and supply decoupling are fully incorporated in the BGW200EG resulting in a low height, small form factor implementation of the complete 802.11b function from the host interface to the antenna(s).

#### 2. **Features**

#### 2.1 General

- Plug-and-play IEEE Std 802.11b 1999 WLAN System-in-Package (SiP)

- Includes all the baseband and radio functions, from host interface up to antenna, needs only external antenna and reference clock

- Support for IEEE 802.11e and Wi-Fi Multi Media (WMM) quality of service enhancements (see Section 2.6)

- Support for IEEE 802.11i and Wi-Fi Protected Access (WPA) security enhancements

- Zero host load; all WLAN functionality is implemented by the BGW200EG

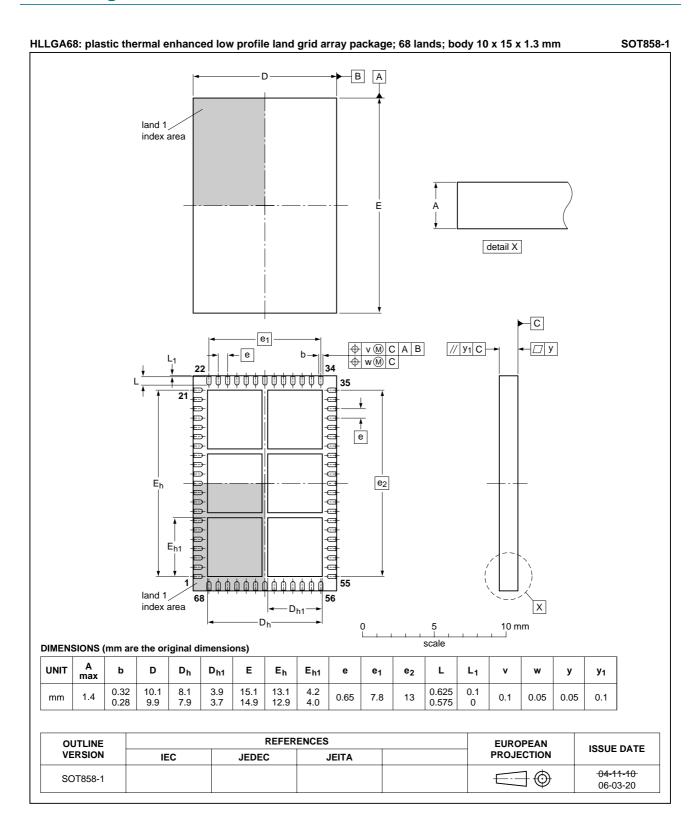

- Small dimensions (10 mm × 15 mm × 1.3 mm) HLLGA68 package

- Lead-free package, RoHS 2006 compliant

- Moisture sensitivity level 4

- Ambient temperature: -30 °C to +85 °C

# 2.2 Power management

- Supply voltage range:

- ◆ Radio transceiver: 2.7 V to 3.0 V (can be extended to V<sub>DD(PA)</sub> + 0.6 V)

- Power amplifier: 2.7 V to 3.0 V

- Baseband digital parts: 1.65 V to 1.95 V

- ◆ Baseband analog parts: 2.7 V to 3.0 V (can be extended to V<sub>DD(PA)</sub> + 0.6 V)

- ◆ Baseband peripherals: 2.7 V to 3.0 V (can be extended to V<sub>DD(PA)</sub> + 0.6 V)

- Low power:

- Internal or external low-frequency sleep clock

- Sleep power consumption: 200 μW (typical)

- Receive power consumption: 480 mW (typical)

- Transmit power consumption (17 dBm output): 750 mW (typical)

#### 2.3 Radio transceiver

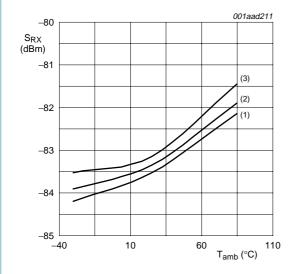

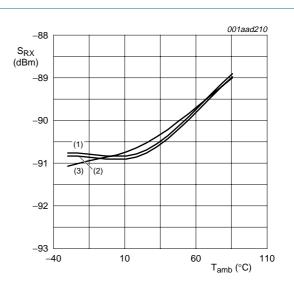

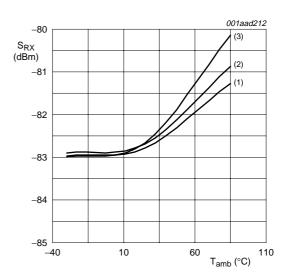

- Receiver sensitivity (Packet Error Rate: PER = 8 %) at 11 Mbit/s data rate: -83 dBm

- Receiver maximum input power: 0 dBm

- RX blocking filter for suppression of Global System for Mobile communication (GSM) and Data Communication System (DCS) interference signals

- Receiver RF antenna diversity fully supported

- Transmitter maximum output power: 17 dBm (with 15 dB adjustable gain)

- Transmitter Error Vector Magnitude (EVM) for 11 Msymbol/s QPSK modulation: 17 % (RMS)

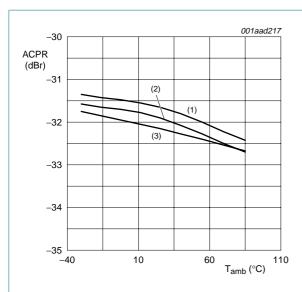

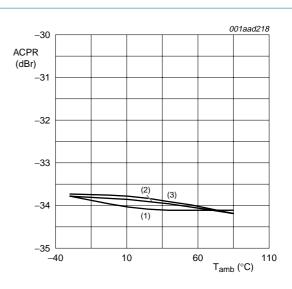

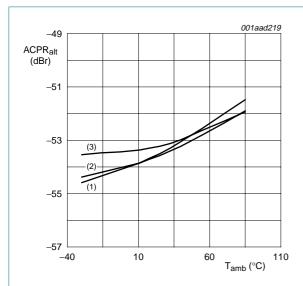

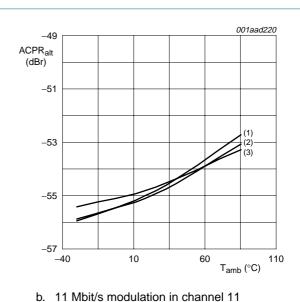

- Transmitter FCC compliant spurious emission spectrum:

- Optional output power software back-off to guarantee FCC compliance in application for low data rates in channel 1 and channel 11

- External filter required for 2nd harmonic suppression

- Internal shielding for better ElectroMagnetic Interference (EMI) immunity

#### 2.4 Baseband hardware

- IEEE 802.11b PHY and MAC:

- ◆ Decision feedback equalizer with > 200 ns multipath delay spread tolerance

- Antenna diversity fully supported

- Data rates up to 11 Mbit/s

- ♦ WEP, TKIP, CCM and AES encryption and decryption engines

- Bluetooth coexistence interface:

- ◆ Interfaces to a range of NXP Semiconductors Bluetooth modules

- Hardware functionality to facilitate connection to 3rd-party Bluetooth solutions

- Hardware support for IEEE 802.15.2 packet traffic arbitration recommendations

- Embedded 32-bit microcontroller:

- ◆ ARM7TDMI-S RISC controller featuring low mW/MHz

- Up to 66 MHz core clock speed at 1.8 V supply voltage

- Instruction pre-fetch unit for improved performance

- Embedded nonvolatile memory: 256-kbit ROM

- ◆ Embedded volatile memory: 5 × 256-kbit SRAM

- JTAG compliant in-circuit emulation interface

- Microcontroller peripherals:

- SPI master/slave interface

- SPI high-speed slave interface with DMA controller

- ◆ SDIO interface with support for SPI, SD1 and SD4 modes

- ◆ 11 general-purpose I/O pins

- UART

- Five 32-bit system timers

- Watchdog timer

IEEE 802.11b System-in-Package

### 2.5 Software

- Microcontroller firmware

- IEEE 802.11b/e/i protocol firmware (see Section 2.6)

- WPA and WMM1 protocol firmware (see Section 2.6)

- Host drivers for the following operating systems:

- ♦ WinCE 4.2/5.0

- ◆ Embedded Linux

- Configuration utility

#### 2.6 Reference

The MAC implemented in the SA2443A is fully compliant with the relevant parts of the published IEEE 802.11 standard and further enhanced with changes detailed in the IEEE 802.11b published amendment. The MAC has also been designed to support the soon to be published IEEE 802.11e amendment as well as the proposed WMM1 standard. The flexible architecture should allow incorporation of any further changes to these amendments and proposed standards before ratification and publication.

#### **Applications** 3.

Product data sheet

Downloaded from Arrow.com.

- IEEE 802.11b WLAN

- Smart phone or feature phone with embedded WLAN

- Personal Digital Assistant (PDA) with embedded WLAN

- Voice over IP (VoIP) cordless phone

- Mobile gaming

#### **Ordering information** 4.

Table 1. **Ordering information**

| Type number | Package |                                                                                                           |          |  |  |  |

|-------------|---------|-----------------------------------------------------------------------------------------------------------|----------|--|--|--|

|             | Name    | Description                                                                                               | Version  |  |  |  |

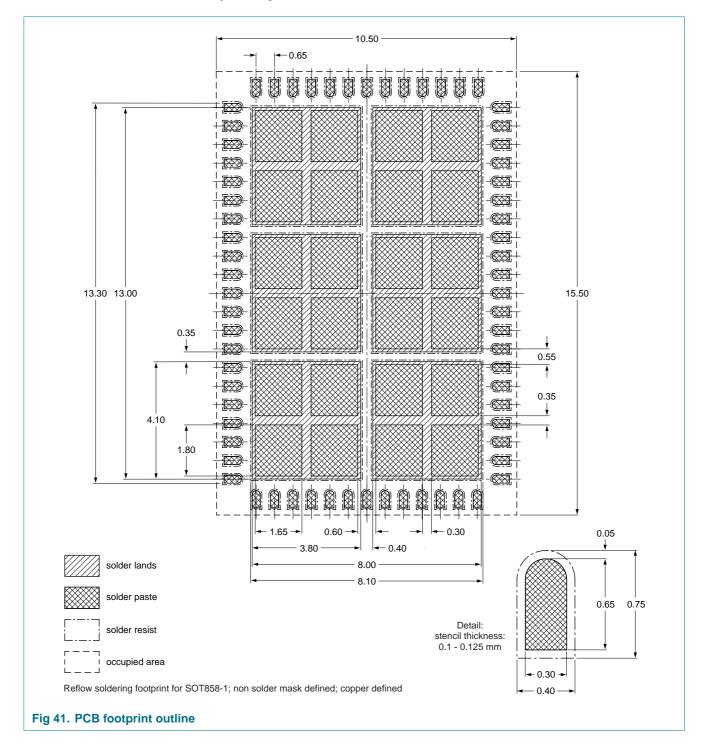

| BGW200EG/01 | HLLGA68 | plastic thermal enhanced low profile land grid array package; 68 lands; body $10 \times 15 \times 1.3$ mm | SOT858-1 |  |  |  |

IEEE 802.11b System-in-Package

#### **5**. **Block diagram**

BGW200EG\_1 © NXP B.V. 2007. All rights reserved. Rev. 01 — 18 July 2007

IEEE 802.11b System-in-Package

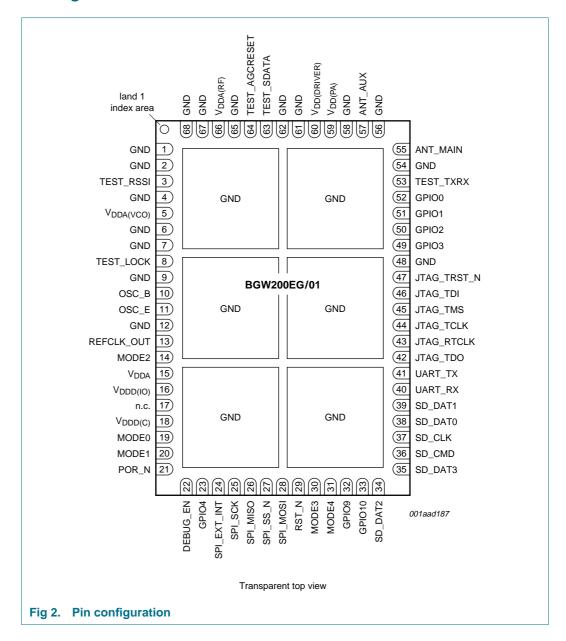

# **Pinning information**

# 6.1 Pinning

# 6.2 Pin description

Table 2. Pin description

| Symbol           | Pin | Type   | Circuit                                            | Reset[1]     | Supply                     | Description                                                                   |

|------------------|-----|--------|----------------------------------------------------|--------------|----------------------------|-------------------------------------------------------------------------------|

| SPI interface    |     |        |                                                    |              |                            |                                                                               |

| SPI_SCK          | 25  | I/O; I | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$              | SPI clock; bidirectional; 32 kHz sleep clock input                            |

| SPI_SS_N         | 27  | I; I/O | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$              | SPI slave select input;<br>general-purpose I/O bit 6;<br>bidirectional        |

| SPI_EXT_INT      | 24  | O; I/O | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$              | SPI external interrupt output;<br>general-purpose I/O bit 5;<br>bidirectional |

| SPI_MISO         | 26  | I/O    | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$              | SPI data (master in / slave out); bidirectional                               |

| SPI_MOSI         | 28  | I/O    | 3-state; 1 ns slew rate;<br>4 mA; CMOS             | I, pull-down | $V_{DDD(IO)}$              | SPI data (master out / slave in); bidirectional                               |

| SDIO Interface   |     |        |                                                    |              |                            |                                                                               |

| SD_CLK           | 37  | l; l   | CMOS; hysteresis                                   | -            | $V_{DDD(IO)}$              | SD clock input; 32 kHz clock input                                            |

| SD_CMD           | 36  | I/O    | 3-state; 1 ns slew rate;<br>4 mA; CMOS             | I            | $V_{DDD(IO)}$              | SD command; bidirectional                                                     |

| SD_DAT0          | 38  | I/O    | 3-state; 1 ns slew rate;<br>4 mA; CMOS             | I            | $V_{DDD(IO)}$              | SD data bit 0; bidirectional                                                  |

| SD_DAT1          | 39  | I/O    | 3-state; 1 ns slew rate;<br>4 mA; CMOS             | I            | $V_{DDD(IO)}$              | SD data bit 1; bidirectional                                                  |

| SD_DAT2          | 34  | I/O    | 3-state; 1 ns slew rate;<br>4 mA; CMOS             | I            | $V_{DDD(IO)}$              | SD data bit 2; bidirectional                                                  |

| SD_DAT3          | 35  | I/O    | 3-state; 1 ns slew rate;<br>4 mA; CMOS             | I, pull-up   | $V_{DDD(IO)}$              | SD data bit 3; bidirectional                                                  |

| UART interface   |     |        |                                                    |              |                            |                                                                               |

| UART_RX          | 40  | I; I/O | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$              | UART receive input;<br>general-purpose I/O bit 7;<br>bidirectional            |

| UART_TX          | 41  | O; I/O | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$              | UART transmit output;<br>general-purpose I/O bit 8;<br>bidirectional          |

| Antenna RF ports |     |        |                                                    |              |                            |                                                                               |

| ANT_MAIN         | 55  | I/O    | analog                                             | -            | -                          | RF main antenna port; 50 $\Omega$                                             |

| ANT_AUX          | 57  | I      | analog                                             | -            | -                          | RF auxiliary antenna port; 50 $\boldsymbol{\Omega}$                           |

| Test pins        |     |        |                                                    |              |                            |                                                                               |

| TEST_RSSI        | 3   | 0      | analog; C <sub>L</sub> = 100 pF                    | LOW          | $V_{DDA(RF)}$              | test pin for RF RSSI signal output                                            |

| TEST_LOCK        | 8   | 0      | CMOS; 4.5 mA                                       | LOW          | $V_{DDA}$                  | test pin for synthesizer lock indicator                                       |

| TEST_TXRX        | 53  | 0      | push-pull; 3 ns slew rate;<br>4 mA                 | LOW          | $V_{DDD(IO)}$              | test pin for RF transmit/receive select signal                                |

| TEST_SDATA       | 63  | I/O    | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$ or $V_{DDA}$ | test pin for 3-wire bus data;<br>bidirectional                                |

| 3GW200EG_1       |     |        |                                                    |              |                            | © NXP B.V. 2007. All rights reserv                                            |

Table 2.

Pin description ...continued

|                       |         | Tuno      |                                                    | Deset[1]     | Cummba               | Description                                                                                          |

|-----------------------|---------|-----------|----------------------------------------------------|--------------|----------------------|------------------------------------------------------------------------------------------------------|

| Symbol                | Pin     | Туре      | Circuit                                            | Reset[1]     | Supply               | Description                                                                                          |

| TEST_AGCRESET         | 64      | 0         | push-pull; 3 ns slew rate;<br>4 mA                 | LOW          | $V_{DDD(IO)}$        | test pin for RF AGC reset;<br>output                                                                 |

| REFCLK_OUT            | 13      | 0         | CMOS                                               | -            | $V_{DDA}$            | test pin for 44 MHz clock outpu                                                                      |

| Bluetooth coexiste    | nce in  | iterface  |                                                    |              |                      |                                                                                                      |

| GPIO0                 | 52      | O; O; I/O | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$        | WLAN arbitration signal output;<br>HW MAC CCA output;<br>general-purpose I/O bit 0;<br>bidirectional |

| GPIO1                 | 51      | I; I/O    | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$        | BT arbitration signal input;<br>general-purpose I/O bit 1;<br>bidirectional                          |

| GPIO2                 | 50      | I; I/O    | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$        | BT high priority traffic indicator input; general-purpose I/O bit 2 bidirectional                    |

| GPIO3                 | 49      | O; I/O    | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$        | WLAN receive indicator output;<br>general-purpose I/O bit 3;<br>bidirectional                        |

| <b>GPIO</b> interface |         |           |                                                    |              |                      |                                                                                                      |

| GPIO9                 | 32      | I/O       | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$        | general-purpose I/O bit 9; bidirectional                                                             |

| GPIO10                | 33      | I/O       | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$        | general-purpose I/O bit 10; bidirectional                                                            |

| JTAG and debug in     | nterfac | е         |                                                    |              |                      |                                                                                                      |

| JTAG_TCLK             | 44      | ı         | CMOS; hysteresis; pull-up                          | -            | $V_{DDD(IO)}$        | JTAG clock input                                                                                     |

| JTAG_RTCLK            | 43      | 0         | push-pull; 3 ns slew rate; 4 mA                    | LOW          | $V_{DDD(IO)}$        | synchronized JTAG clock output                                                                       |

| JTAG_TMS              | 45      | I         | CMOS; hysteresis; pull-up                          | -            | $V_{DDD(IO)}$        | JTAG test mode select input                                                                          |

| JTAG_TRST_N           | 47      | I         | CMOS; hysteresis; pull-up                          | -            | $V_{DDD(IO)}$        | JTAG reset input; active LOW                                                                         |

| JTAG_TDI              | 46      | I         | CMOS; hysteresis; pull-up                          | -            | $V_{DDD(IO)}$        | JTAG test data input                                                                                 |

| JTAG_TDO              | 42      | 0         | 3-state; 3 ns slew rate;<br>4 mA                   | high-Z       | $V_{DDD(IO)}$        | JTAG test data output                                                                                |

| DEBUG_EN              | 22      | I         | CMOS; hysteresis; pull-down                        | -            | $V_{DDD(IO)}$        | debug enable input                                                                                   |

| Miscellaneous         |         |           |                                                    |              |                      |                                                                                                      |

| OSC_B                 | 10      | ļ         | analog                                             | -            | $V_{DDA}$            | crystal oscillator / buffer input                                                                    |

| OSC_E                 | 11      | 0         | analog                                             | -            | $V_{DDA}$            | crystal oscillator output                                                                            |

| GPIO4                 | 23      | I; I/O    | 3-state; 3 ns slew rate;<br>4 mA; CMOS; hysteresis | I, pull-down | $V_{DDD(IO)}$        | 32 kHz sleep clock input;<br>general-purpose I/O bit 4;<br>bidirectional                             |

| RST_N[2]              | 29      | ļ         | CMOS; hysteresis                                   | -            | $V_{DDD(IO)}$        | system reset input; active LOW                                                                       |

| POR_N                 | 21      | 0         | push-pull; 3 ns slew rate; 4 mA                    | LOW          | $V_{DDD(IO)}$        | power-on reset output; active LOW                                                                    |

| MODE0                 | 19      | I         | CMOS; hysteresis                                   | -            | $V_{DDD(IO)}$        | load source 0 input                                                                                  |

| MODE1                 | 20      | I         | CMOS; hysteresis                                   | -            | V <sub>DDD(IO)</sub> | load source 1 input                                                                                  |

| MODE2                 | 14      | -         | connected to ground                                | -            | -                    | reserved for pin-compatibility with BGW211                                                           |

| DCM/000EC 4           |         |           |                                                    |              |                      | © NIVE D.V. COOT. *** · · ·                                                                          |

BGW200EG\_1 © NXP B.V. 2007. All rights reserved.

# IEEE 802.11b System-in-Package

Table 2. Pin description ...continued

| Symbol                  | Pin | Type | Circuit       | Reset[1] | Supply | Description                                |

|-------------------------|-----|------|---------------|----------|--------|--------------------------------------------|

| MODE3                   | 30  | -    | not connected | -        | -      | reserved for pin-compatibility with BGW211 |

| MODE4                   | 31  | -    | not connected | -        | -      | reserved for pin-compatibility with BGW211 |

| n.c.                    | 17  | -    | not connected | -        | -      | reserved for pin-compatibility with BGW211 |

| Power supplies          |     |      |               |          |        |                                            |

| V <sub>DDA(VCO)</sub>   | 5   | -    | -             | -        | -      | VCO analog supply voltage                  |

| $V_{DDA}$               | 15  | -    | -             | -        | -      | analog supply voltage                      |

| $V_{DDD(IO)}$           | 16  | -    | -             | -        | -      | I/O digital supply voltage                 |

| $V_{DDD(C)}$            | 18  | -    | -             | -        | -      | core digital supply voltage                |

| $V_{DD(PA)}$            | 59  | -    | -             | -        | -      | power amplifier supply voltage             |

| V <sub>DD(DRIVER)</sub> | 60  | -    | -             | -        | -      | driver supply voltage                      |

| $V_{DDA(RF)}$           | 66  | -    | -             | -        | -      | RF analog supply voltage                   |

| GND                     | 1   | -    | -             | -        | -      | ground                                     |

| GND                     | 2   | -    | -             | -        | -      | ground                                     |

| GND                     | 4   | -    | -             | -        | -      | ground                                     |

| GND                     | 6   | -    | -             | -        | -      | ground                                     |

| GND                     | 7   | -    | -             | -        | -      | ground                                     |

| GND                     | 9   | -    | -             | -        | -      | ground                                     |

| GND                     | 12  | -    | -             | -        | -      | ground                                     |

| GND                     | 48  | -    | -             | -        | -      | ground                                     |

| GND                     | 54  | -    | -             | -        | -      | ground                                     |

| GND                     | 56  | -    | -             | -        | -      | ground                                     |

| GND                     | 58  | -    | -             | -        | -      | ground                                     |

| GND                     | 61  | -    | -             | -        | -      | ground                                     |

| GND                     | 62  | -    | -             | -        | -      | ground                                     |

| GND                     | 65  | -    | -             | -        | -      | ground                                     |

| GND                     | 67  | -    | -             | -        | -      | ground                                     |

| GND                     | 68  | -    | -             | -        | -      | ground                                     |

<sup>[1]</sup> I = input mode.

<sup>[2]</sup> The RST\_N pin should be linked to the POR\_N pin; use of an external reset signal is not supported.

# 7. Functional description

### 7.1 General

The BGW200EG contains the following parts in one SiP (with embedded software):

- IEEE 802.11b RF transceiver

- IEEE 802.11b compliant modem

- IEEE 802.11b MAC

- ARM7TDMI-S microcontroller

- Static RAM (SRAM)

- Interface circuits

- Power management circuit

Together with a reference clock and antenna with harmonic filter, this device forms a complete WLAN solution. The system architecture is ideal for mobile products and requires no load on the host processor. The host sleeps while the WLAN listens for the beacon and is woken by the WLAN when appropriate.

The BGW200EG is designed to be used for wireless links operating in the globally available ISM band, between 2402 MHz and 2497 MHz. The radio part is composed of a fully integrated, state-of-the-art, direct conversion transceiver chip, a linear power amplifier chip, an RX antenna filter for out-of-band blocking, TX/RX and antenna diversity switches, TX and RX baluns and a basic amount of supply decoupling. The SiP radio circuit is integrated on an organic substrate. The total WLAN system is integrated in a 10 mm  $\times$  15 mm HLLGA68 package and can be handled as a standard pick-and-place component. The device is a 'plug-and-play' SiP. Robust design requires no manufacturing trimming, resulting in a cost-optimized solution. The RF antenna ports have a normalized 50  $\Omega$  impedance and each can be connected directly to an external antenna with a 50  $\Omega$  transmission line.

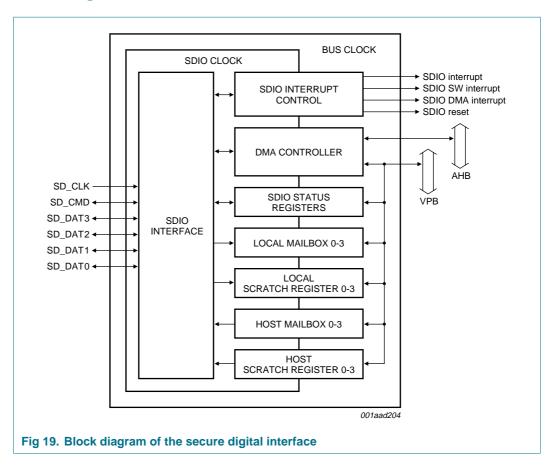

The BGW200EG supports two host interfaces. The high-speed SPI slave (SPI2) interface is ideal for embedded applications since only 5 signal lines are required to connect to the host controller, and the protocol for this interface has a low processing overhead. The SDIO interface can operate in SPI, SD1 and SD4 modes, and can be used in an embedded application or in a secure digital NIC card. The ARM7TDMI-S RISC core, today considered as the standard RISC processor in the telecommunications industry, is integrated in the SA2443A. The processor is characterized by its extremely low mW/MIPS ratio. The BGW200EG has 1 Mbit of on-chip SRAM, thereby eliminating the need for external SRAM. This reduces the total footprint of the WLAN solution as well as the power consumption of the system. The functionality of the IEEE 802.11 MAC is split between hardware and software running on the ARM microcontroller. The IEEE 802.11b modem is implemented in hardware with control and configuration handled by software.

The BGW200EG is designed to be used as a low-cost, low-power wireless LAN link. Existing WLAN solutions, aimed at the computing market, have made use of the host processor to implement such functions as fragmentation and defragmentation. The BGW200EG implements all WLAN functions internally (implemented in either hardware or firmware) with the result that there is no processing load on the host controller. This link

will be the basis for smart phones and PDAs to communicate with a LAN network through a WLAN access point both for voice (VoIP) and data access. It is designed to handle the IEEE 802.11b specification.

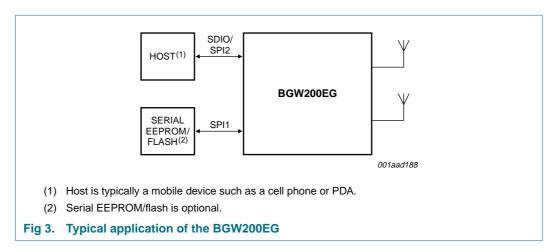

The BGW200EG combines the IEEE 802.11b PHY and MAC with the embedded HCI firmware for selected host operating systems through either the SPI or SDIO interfaces. A typical example of the BGW200EG in its environment is illustrated in Figure 3. Together with an antenna, reference clock and filtering as required by the application, this device forms a complete WLAN solution. The system architecture is ideal for mobile products and requires no load on the host processor. The host sleeps while the WLAN listens for the beacon and is woken by the WLAN when appropriate.

#### 7.2 Subblock overview

Table 3 gives an overview of some subblocks shown in Figure 1 and provides a reference to the section of the data sheet that describes these blocks.

**Subblock overview** Table 3.

| Block name        | Description                                                        | Reference    |

|-------------------|--------------------------------------------------------------------|--------------|

| SA2405 RF transce | iver                                                               |              |

| FIRDAC            | finite impulse response digital-to-analog converter                | Section 8    |

| AGC state machine | automatic gain control state machine                               |              |

| RSSI              | receive signal strength indicator                                  |              |

| SA2411 RF power a | amplifier                                                          |              |

| PA                | power amplifier                                                    | Section 9    |

| SA2443A Baseband  | d/MAC                                                              |              |

| SCU               | system configuration unit                                          | Section 10.1 |

| Processor:        |                                                                    |              |

| ARM7TDMI-S        | fast RISC processor controlling other blocks via AHB and VPB buses | Section 10.2 |

| IPU               | instruction pre-fetch unit                                         |              |

| JTAG              | joint test action group interface for ARM7 emulation               |              |

| SRAM              | system RAM for use by firmware                                     |              |

| ROM               | read only program memory                                           |              |

BGW200EG 1 © NXP B.V. 2007. All rights reserved. Rev. 01 — 18 July 2007

IEEE 802.11b System-in-Package

Subblock overview ...continued Table 3.

| Block name | Description                                           | Reference     |

|------------|-------------------------------------------------------|---------------|

| MAC:       |                                                       |               |

| HW MAC     | hardware medium access control layer                  | Section 10.3  |

| PHYTX      | physical layer transmitter                            | Section 10.7  |

| PHYRX      | physical layer receiver                               | Section 10.8  |

| WEP        | WEP encryption and decryption engine                  | Section 10.4  |

| AES (CCM)  | CCM encryption and decryption engine                  | Section 10.5  |

| DMA        | general-purpose DMA engine                            | Section 10.6  |

| RFIF       | RF interface                                          | Section 10.9  |

| TIMERS     | system timers                                         | Section 10.10 |

| ICU        | interrupt control unit                                | Section 10.11 |

| UART       | universal asynchronous receiver/transmitter interface | Section 10.12 |

| SPI:       |                                                       |               |

| SPI1       | master/slave serial peripheral interface              | Section 10.13 |

| SPI2       | high-speed slave serial peripheral interface          | Section 10.14 |

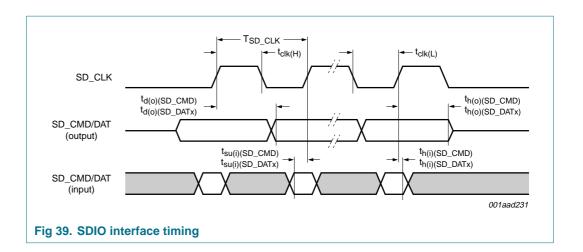

| SDIO       | secure digital input/output interface                 | Section 10.15 |

| GPIO       | general-purpose input/output pin(s)                   | Section 10.16 |

#### SA2405 RF transceiver 8.

The SA2405 RF transceiver is targeted for operation in the 2.45 GHz band, specifically for IEEE 802.11b 1 Mbit/s and 2 Mbit/s DSSS, and 5.5 Mbit/s and 11 Mbit/s CCK high rate standards.

The RF VCO is common to both the transmitter and the receiver. The RF VCO is a differential 4.8 GHz Local Oscillator (LO) with the frequency determining components internal to the IC. The VCO is connected internally to a frequency divider and a quadrature generator circuit which produces the local oscillator frequencies for the I and Q up mixers and down mixers. The divider output is also internally connected to the synthesizer which can be programmed in order to produce the desired LO frequency. The frequency step size of the synthesizer is 0.5 MHz.

The RF LNA has two stepped gains controlled internally by the on-chip AGC control loop. The RF signal is downconverted to baseband by the quadrature mixers. The I and Q low-pass filters are fully integrated active Type I Chebychev filters. The I/Q pass band extends from DC to a -3 dB corner at 7 MHz. Three stepped gains are incorporated in the channel filters. Additional adjustable gain is provided in baseband amplifiers to achieve a totally adjustable gain range of 90 dB. The RX output to the baseband are differential I and Q signals.

The RX chain also integrates a high-pass filter (DC notch) for cancellation of the DC offset inherent to zero-IF architecture. The high-pass filter has a programmable lower 3 dB cut-off frequency of 10 MHz, 1 MHz, 100 kHz or 10 kHz. The DC offset cancellation occurs simultaneously with the on-chip AGC loop settling process. During the AGC settling phase, the high-pass cut-off frequency is dynamically selected between 10 MHz and 1 MHz to quickly reduce DC offset values from +50 dBc to below -20 dBc relative to a -76 dBm input signal at the antenna.

After the AGC settling (may be more than one AGC cycle with antenna diversity), the high-pass is configured to 100 kHz for 5 µs before switching to a final 10 kHz cut-off frequency. The low value of 10 kHz is required for minimizing the signal distortion created by a high-pass function at zero frequency. The high-pass will then remain set to the 10 kHz cut-off frequency until a new AGC cycle for the next receive data burst is started. Whenever there is a frequency change in the high-pass filter lower cut-off, the DC offset can change from a very low value to approximately 50 % (1 MHz ≥ 100 kHz step) or 10 % (100 kHz ≥ 10 kHz step) of the signal level. This DC offset then decays according to the high-pass response of the filter.

The receiver contains a fully integrated automatic gain control loop. It works by adjusting the internal gain such that the RX output amplitude meets a predefined target value. A measured RSSI is used to realize the gain adjustment. By default, the AGC is always set to a default maximum gain (adjustable by register value GMAX) whenever the BGW200EG enters the receive mode of operation from another operational mode. The receiver takes 5 µs to settle after entering the receive mode, which includes the time for DC offsets to be removed with a 1 MHz lower cut-off frequency of the high-pass filtering. This lower cut-off frequency of 1 MHz remains unchanged as long as the AGC remains in the default maximum gain state. By successively reducing the gain from its initial maximum value, the AGC loop searches for the correct gain value to provide a nominal RX output amplitude to the baseband. This is achieved after a maximum of 8 µs with the default wait periods. This settling time is determined by wait periods necessary to settle the receiver after gain switching actions. The individual wait periods can be adjusted by means of register settings.

The Receive Signal Strength Indicator (RSSI) is implemented as an error signal derived from comparing the signal level at the RX output to a nominal value. The RSSI acts on the modulated RF signal envelope that is extracted from the baseband I and Q signals, and reflects on a logarithmic scale the amplitude of the instantaneous modulated RF signal envelope. The RSSI signal is filtered by a 3rd-order Bessel low-pass filter with 0.5 MHz cut-off frequency. The RSSI signal will include DC offsets and will, therefore, show transient decaying errors when the DC cancellation corner frequency is changed.

The receiver is designed to exceed the 802.11 specifications for the blocking and intermodulation. It can accept continuous or randomly pulsed interference single signals or multitone signals that are more than 35 dB stronger than the required signal and up to -10 dBm of interference level. The spurious I and Q outputs are maintained to less than -20 dBc of the required signal level.

The transmitter input binary data streams are sampled with a 44 MHz reference clock and integrated FIRDACs provide additional pulse shaping filtering. The wideband I/Q up converter includes reconstruction filters (4th order low-pass Butterworth with 9.75 MHz 3 dB upper cut-off frequency). At 18 dBm maximum transmitter output level, the out-of-band (FCC forbidden band) spurious signal power is less than -77 dBc (integrated over 1 MHz with a 100 kHz resolution bandwidth) for the 11 Msymbol/s CCK modulation.

By using the on-chip calibration loop the transmitter carrier leakage can be reduced to levels far less than required by the standard. An RF power meter detects the LO level, converts it into a digital signal and a state machine determines the compensation values which are fed through an on-chip DAC directly to the I/Q inputs. The I/Q gain and phase imbalance, the InterSymbol Interference (ISI) of the reconstruction filter and in-channel noise produce a typical modulation EVM of less than 8 % (RMS) for 11 Msymbol/s CCK modulation.

Upon entering the TX mode, the ramping-up of the RF TX signal is delayed by an internal power ramping circuit. The ramping-up time is fixed while the delay prior to ramping-up can be programmed by register settings. There is 15 dB of gain control with 1 dB resolution. A gain adjustment range of 0 dB to 7 dB in 1 dB steps is provided in the TX reconstruction filter. An additional 8 dB of gain control is provided in the upconverters via a single 8 dB gain step.

# 9. SA2411 RF power amplifier

The power stage of the transmit amplifier is a fixed gain, class AB amplifier designed to give typically 18 dBm output power at the antenna pin for an 11 Msymbol/s CCK modulation. The device has differential inputs and an integrated balun and harmonic filter at the output. The integrated power detector detects the power level and transforms it into a low-frequency voltage input for the baseband.

# 10. SA2443A IEEE 802.11b medium access controller and modem

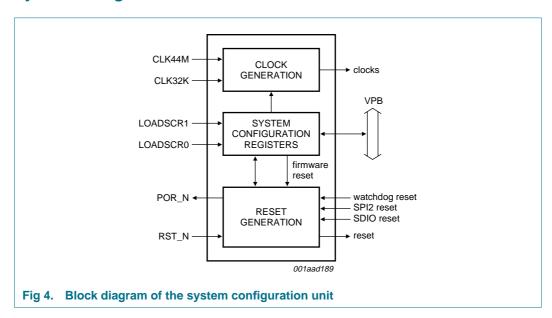

# 10.1 System configuration unit

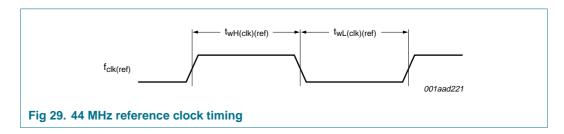

The 44 MHz reference clock for the SA2443A is supplied by the SA2405.

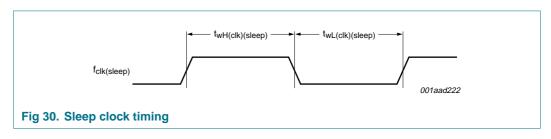

Power consumption is substantially reduced in doze mode using a low-frequency sleep clock. The sleep clock can be derived from an internal 1 MHz oscillator, located in the clock generation block, or supplied externally (typically 32 kHz).

The clock generation block generates all clocks required by the SA2443A from the 44 MHz, 1 MHz and 32 kHz clocks. The microcontroller and bus clock frequency can be configured between 32 kHz and 66 MHz to allow power consumption to be optimized.

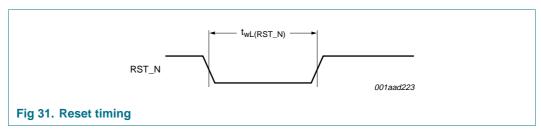

The SA2443A has five reset sources:

- External reset (pin RST\_N)

- · Watchdog timer reset

- Firmware reset

- SPI2 reset

- SDIO reset

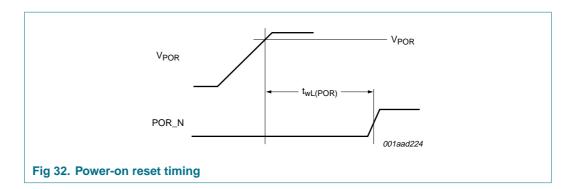

A power-on reset signal is generated when the core supply voltage is applied. The reset signal remains active for 4 ms after the 1.8 V supply is stable. The signal is available on pin POR\_N. The RST\_N pin should be linked to the POR\_N pin; use of an external reset signal is not supported.

The MODE0 and MODE1 pins are used to control the boot mode of the SA2443A as shown in Table 4.

SA2443A boot modes Table 4.

| MODE0 | MODE1 | Boot mode     | Description                                | Boot clock |

|-------|-------|---------------|--------------------------------------------|------------|

| L     | L     | SPI embedded  | firmware download from the host via SPI2   | 44 MHz     |

| Н     | L     | SPI flash     | firmware read from a serial flash via SPI1 |            |

| L     | Н     | SDIO embedded | firmware download from the host via SDIO   |            |

| Н     | Н     | reserved      | -                                          | -          |

The SPI embedded boot mode is used when the WLAN solution is embedded in an application, such as a cellular phone or PDA. In this case, the SA2443A firmware will be downloaded from the host processor via the high-speed SPI slave interface (SPI2).

The SPI flash mode is used primarily for firmware development and debugging. In this mode, firmware is read from a serial flash memory connected to the master/slave SPI interface (SPI1).

The SDIO embedded mode operates in the same way as the SPI embedded mode, except that code is downloaded from the SDIO interface.

IEEE 802.11b System-in-Package

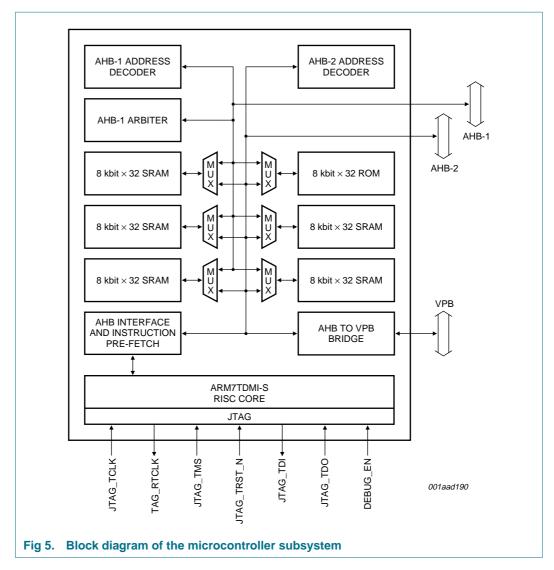

# 10.2 Microcontroller subsystem

The microcontroller subsystem is based around an ARM7TDMI-S RISC controller and has the following features:

- Embedded nonvolatile memory: 256-kbit ROM

- Embedded volatile memory: 5 x 256-kbit SRAM

- Instruction pre-fetch unit for enhanced microcontroller performance

- Two high-performance AHB buses for optimized throughput:

- AHB1 is a multimaster bus used for DMA transfers

- AHB2 is a single-master bus used by the microcontroller

- VPB bus for lower-speed peripherals

- JTAG-compliant interface for ARM7 in-circuit emulation (enabled by pulling the DEBUG\_EN pin HIGH)

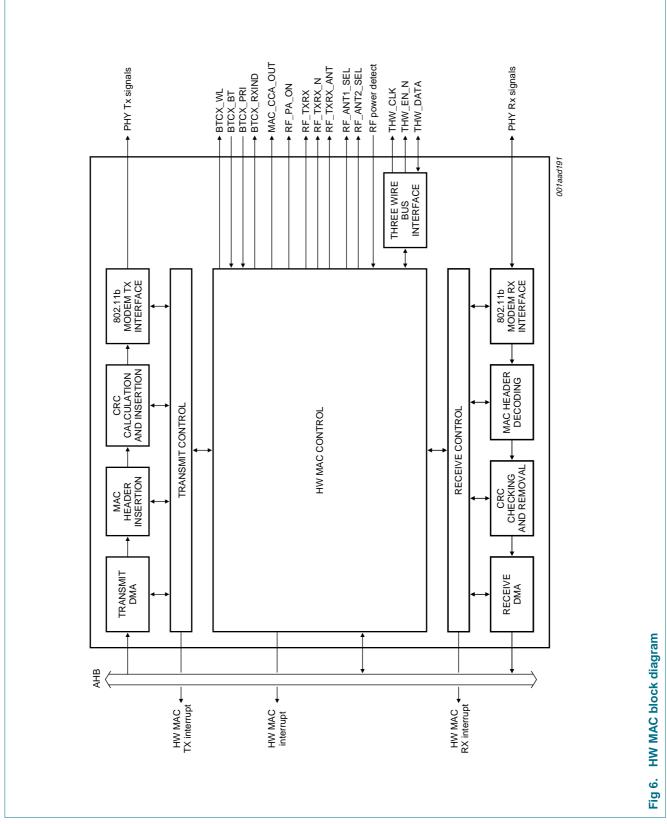

# 10.3 Hardware medium access control layer

The IEEE 802.11b compliant HW MAC supports the following features:

- Data rates up to 11 Mbit/s

- SIFS timer

- Cyclic Redundancy Check (CRC) calculation and checking

- · Back-off mechanism support

- Automated transmit timing control

- Automated TBTT/TXOP boundary checking

- Automated NAV timer update

- · Automated IBSS mode beacon handling

- · Automated TSF update from the beacon packet

- Automated insertion of TSF into the beacon packet

- Automatic wake-up for beacon reception

- Automated header field insertion (e.g. transmit address)

- QoS support:

- 4 EDCF channels

- 2 streams for HCF

- ATIM handler

- SW programmable automated response mechanism (e.g. ACK, RTS, CTS and QoS Null)

- Programmable unicast, multicast and beacon filtering

- · Receive and transmit DMA engines for efficient data transfer

- Configurable TX/RX status interrupts

- Bluetooth coexistence Packet Traffic Arbitration (PTA) support

- Configurable antenna TX/RX and diversity switch control signals

The HW MAC block has the following external interfaces:

- SA2405 2.45 GHz transceiver control interface

- Antenna, TX/RX and diversity switch control signals

- Bluetooth coexistence interface

The HW MAC block has interfaces to the following subblocks:

- Physical layer transmitter (PHYTX); see Section 10.7

- Physical layer receiver (PHYRX); see Section 10.8

- RF interface (RFIF); see Section 10.9

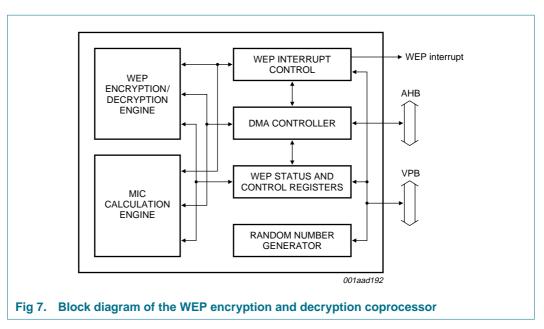

# 10.4 WEP encryption and decryption coprocessor

The WEP encryption and decryption coprocessor has the following features:

- WEP 64-bit and 128-bit encryption and decryption

- WEP2 support in conjunction with firmware running on the microcontroller

- MIC calculation to facilitate TKIP support in conjunction with firmware running on the microcontroller

- DMA controller for high data throughput with minimum processing load on the microcontroller

- Random number generator to assist in the generation of encryption keys

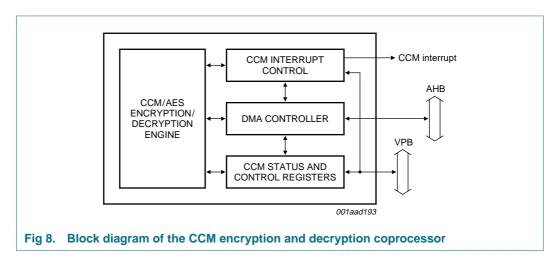

# 10.5 CCM encryption and decryption coprocessor

The CCM encryption and decryption coprocessor supports both the CCM (counter mode with CBC-MAC) and the AES security algorithms. A DMA engine is incorporated to allow high data throughput with minimum loading on the microcontroller.

BGW200EG\_1 © NXP B.V. 2007. All rights reserved.

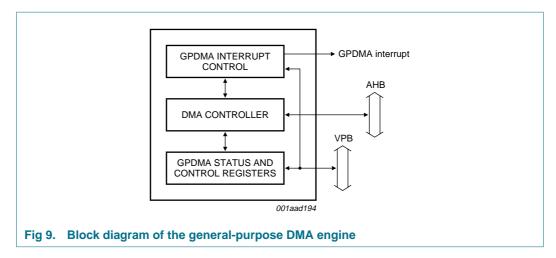

# 10.6 General-purpose DMA engine

The general-purpose DMA engine can be used to move data from one memory location to another with minimum firmware involvement. Uses of the block include fragmentation and defragmentation assistance.

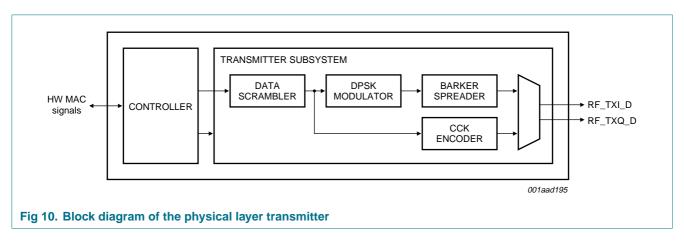

# 10.7 Physical layer transmitter

The PHYTX block is IEEE 802.11b compliant and supports the following features:

- 1 Mbit/s, 2 Mbit/s, 5.5 Mbit/s and 11 Mbit/s data rates

- Short and long preambles

The PHYTX block is tightly coupled to the SA2443A HW MAC block; see <u>Section 10.3</u>. Control and configuration of the PHYTX block are performed by the HW MAC block and firmware.

The PHYTX block comprises the controller and the transmitter subsystem.

The controller is responsible for interfacing with the HW MAC unit, generation of the PLCP header and control of the transmitter subsystem. The controller passes a serial bit stream into the transmitter subsystem. The transmitter subsystem generates modulated I and Q signals compatible with the serial digital transmit interface on the SA2405 transceiver.

BGW200EG\_1 © NXP B.V. 2007. All rights reserved.

IEEE 802.11b System-in-Package

The test modes available with the PHYTX block and their uses are given in Table 5.

Table 5. **PHYTX** test modes

| Test mode | Description                      | Measurement uses          |

|-----------|----------------------------------|---------------------------|

| RANDOM    | continuous modulated random data | EVM, spectral mask        |

| 0101      | continuous 0101 sequence         | carrier suppression       |

| CW        | unmodulated I/Q data             | transmit frequency offset |

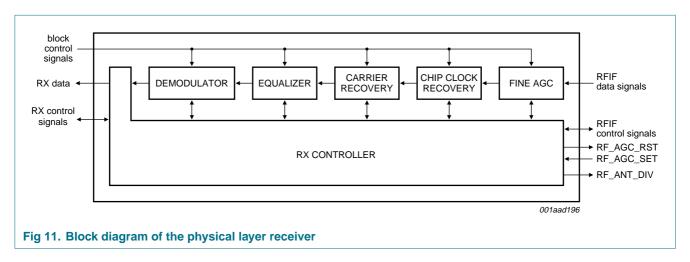

# 10.8 Physical layer receiver

The PHYRX block is IEEE 802.11b compliant and supports the following features:

- 1 Mbit/s, 2 Mbit/s, 5.5 Mbit/s and 11 Mbit/s data rates

- Short and long preambles

- Decision feedback equalizer with > 200 ns RMS multipath delay spread tolerance

- Antenna diversity

The PHYRX block is tightly coupled to the SA2443A HW MAC block; see Section 10.3. Control and configuration of the PHYRX block is performed by the HW MAC block and firmware. The PHYRX also interfaces to the RF interface block; see Section 10.9.

The RX controller contains the state machine that switches the modes of the RX blocks and performs the following functions:

- Clear Channel Assessment (CCA)

- Bit synchronization

- Antenna diversity

The fine AGC block adjusts the received signal level for optimum receiver performance. Sampling clock correction and carrier frequency correction are handled by the chip clock recovery and carrier recovery blocks respectively. Correction for multipath distortion is performed by a fractionally spaced decision feedback equalizer.

IEEE 802.11b System-in-Package

The operation performed by the demodulator is dependent on the data rate. For 1 Mbit/s or 2 Mbit/s rates the demodulator will differentially decode the output of a Barker de-spreader. For 5.5 Mbit/s or 11 Mbit/s data rates a CCK decoder is used to translate the output of the equalizer into data bits. In both cases, a descrambler removes the pseudorandom sequence from the data.

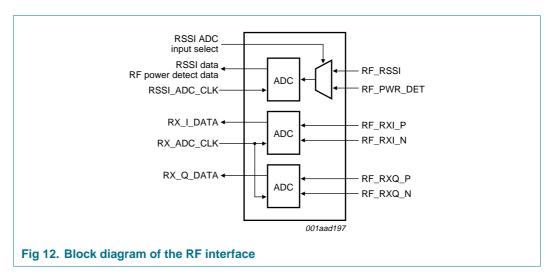

# 10.9 RF interface

The RF interface has the following features:

- RSSI and power detect input:

- 8-bit ADC

- Multiplexed ADC input

- · Analog receive inputs:

- Differential inputs

- 8-bit ADC

Digitized received I/Q signals are routed, together with RSSI values, to the physical layer receiver; see Section 10.8. Power detector samples are routed to the HW MAC; see Section 10.3.

**Product data sheet**

Downloaded from Arrow.com.

# 10.10 System timers

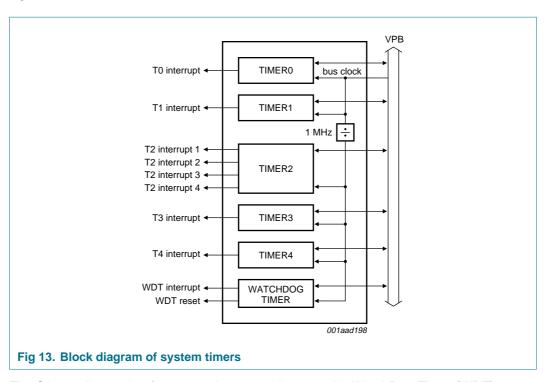

The SA2443A contains five general-purpose timers and a WatchDog Timer (WDT). Table 6 provides an overview of the timer functionality.

Table 6. Timer overview

| Timer name | Туре       | Count frequency | Interrupt conditions                                                                   |

|------------|------------|-----------------|----------------------------------------------------------------------------------------|

| TIMER0     | down count | bus clock       | on zero                                                                                |

| TIMER1     | down count | bus clock       | on zero                                                                                |

| TIMER2     | up count   | 1 MHz           | when count matches any of four programmed values                                       |

| TIMER3     | down count | 1 MHz           | on zero                                                                                |

| TIMER4     | down count | 1 MHz           | on zero                                                                                |

| WDT        | down count | 1 MHz           | interrupt when count matches programmed value; reset generated when count reaches zero |

Timers 0, 1, 3 and 4 can be programmed with a start value. Operation can be either single shot or continuous. An interrupt is generated when a timer counts down to zero.

Timer 2 is programmed with up to four interrupt compare values. An interrupt is generated when the counter value matches one of the interrupt compare values. Operation can be either one shot or continuous.

The watchdog timer provides a mechanism to reset the SA2443A if for some reason the firmware becomes locked. A start value is programmed from which the counter counts down to zero. For correct operation of the SA2443A the firmware must reset the start value before the counter reaches zero. If the counter reaches zero the SA2443A is reset. An interrupt compare value can be programmed, allowing a warning to be generated prior to the full reset.

IEEE 802.11b System-in-Package

# 10.11 Interrupt control unit

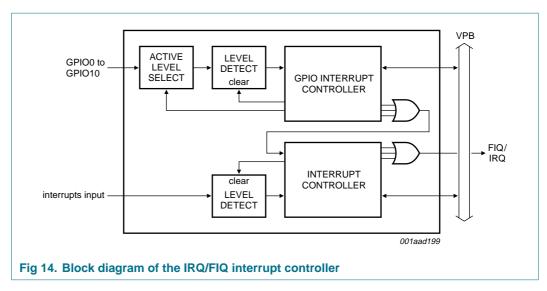

Two primary interrupt controllers are implemented:

- Fast Interrupt reQuest (FIQ) interrupt controller

- Interrupt ReQuest (IRQ) interrupt controller

For each of the primary interrupt controllers there is a secondary GPIO interrupt controller.

The FIQ interrupt controller provides fast, low-latency interrupt handling, whereas the IRQ interrupt controller is used for general interrupts.

For each interrupt controller it is possible to enable or disable individual interrupts, read the status of the interrupts and observe the interrupt input status.

The FIQ and IRQ interrupt controllers also provide a vector register that contains an instruction address that the firmware interrupt handler can jump to. A different address will be reported for each interrupt. In the case of simultaneous interrupts, the vector address will be for the highest priority interrupt. Interrupt 0 is the highest priority and interrupt 31 is the lowest priority.

All interrupts are level sensitive and for GPIO interrupts the active level can be configured by firmware.

IEEE 802.11b System-in-Package

# 10.12 Universal asynchronous receiver transmitter

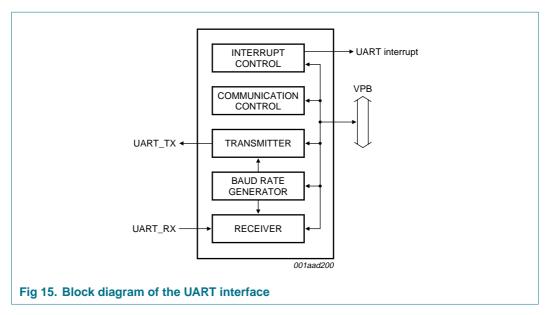

The Universal Asynchronous Receiver Transmitter (UART) supports the following features:

- Parity generation and detection: even, odd, fixed logic 1 or logic 0 or no parity

- Stop bit generation: 1, 1.5 (5-bit character size only) or 2 stop bits

- Character sizes: 5-bit, 6-bit, 7-bit or 8-bit

- Programmable standard baud rates up to 4.125 Mbit/s

- Automatic line error checking: stop bit failure (framing), RX overrun, parity error

- Compatible with the industry standard 16450 UART

The UART provides an asynchronous interface that includes interrupt handling and a baud rate generator allowing 16 times oversampling. The interface supports character formats from 5-bit to 8-bit length with an optional parity bit and 1, 1.5 or 2 stop bits. All standard bit rates are supported.

IEEE 802.11b System-in-Package

# 10.13 Master/slave serial peripheral interface

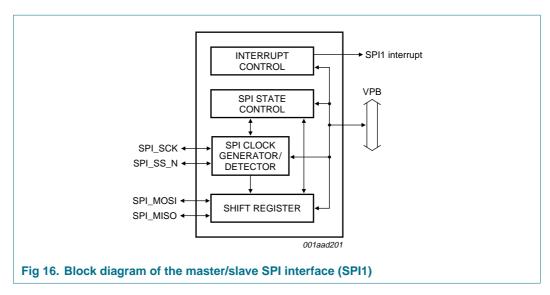

The master/slave SPI interface (SPI1) has the following features:

- Master or slave mode operation

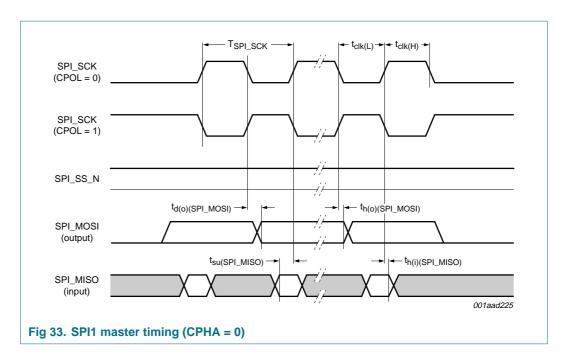

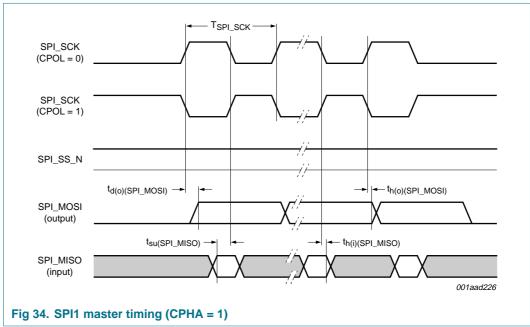

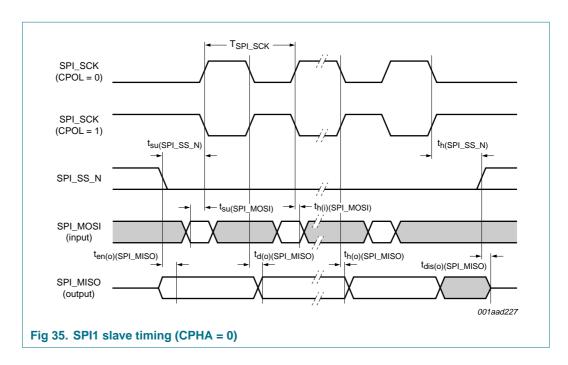

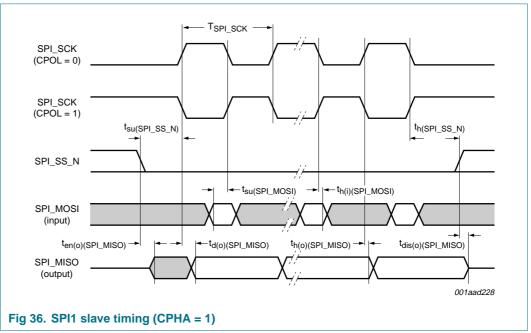

- SPI mode 0 and mode 3 supported in both master and slave modes

- Programmable clock frequency up to 8.25 MHz

- Automatic error checking: write collision, read overrun, mode fault and slave abort

The SPI1 interface block can be configured to work with most SPI master or slave devices. Clock frequency, polarity (bit CPOL) and phase (bit CPHA) are configurable by firmware, as is the data bit order (LSB first or MSB first).

The primary use of the interface is as an SPI master connected to a serial EEPROM or flash memory. In this case, one of the GPIO pins (see Section 10.16) must be controlled by firmware to generate the EEPROM slave select signal. When used in master mode pin SPI SS N must be held HIGH to prevent a mode fault occurring.

The SPI clock is oversampled by a factor of 8. The maximum SPI1 clock frequency is therefore limited to 1/8 of the bus clock.

The I/O pins for this interface are multiplexed with the I/O pins for the SPI2 block; see Section 10.14.

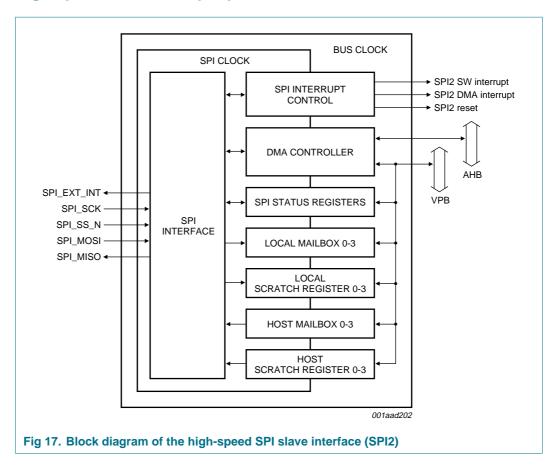

# 10.14 High-speed slave serial peripheral interface

The high-speed SPI slave interface (SPI2) has the following features:

- SPI mode 3 slave interface

- Up to 66 Mbit/s data transfer rate (when SPI\_MOSI is clocked from the positive edge of SPI\_SCK)

- 8-bit minimum packet length

- Half-duplex operation

- DMA controller

- 8 mailboxes (4 local and 4 host)

- 8 scratch registers (4 local and 4 host)

- Low-overhead link protocol

- External signal for interrupting SPI master

- SPI host can reset the SA2443A

The SPI2 interface of the SA2443A is a high-speed SPI slave interface intended for high-throughput host communication.

The I/O pins for this interface are multiplexed with the I/O pins for the SPI1 block; see Section 10.13.

#### 10.14.1 SPI interface

The SPI interface operates entirely in the SPI clock domain. This enables the use of a higher SPI clock frequency than would be allowed with the usual oversampling scheme. SPI2 clock frequencies of up to 66 MHz are allowed.

The SPI\_SCK for SPI2 only needs to run when a data transfer is in progress. No additional clock pulses are needed.

When the SA2443A is the only slave on the SPI bus the SPI\_SS\_N signal can be tied permanently LOW, without any impact on power consumption.

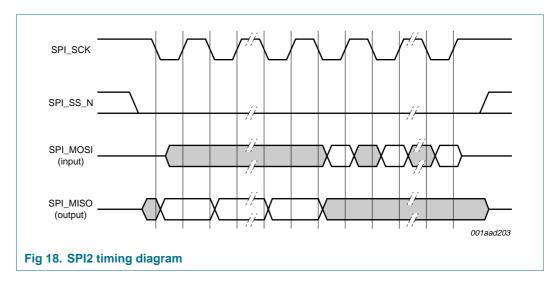

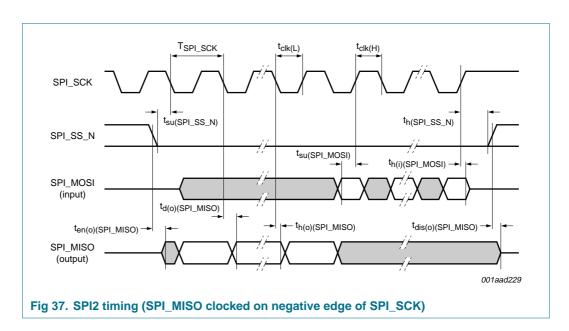

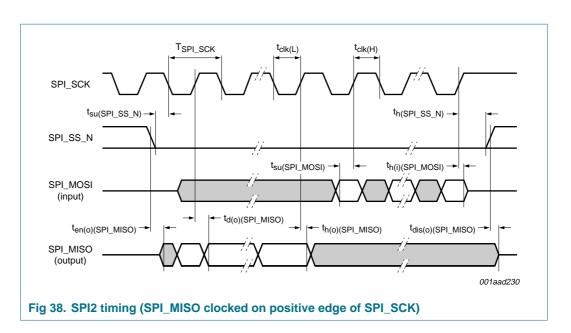

The SPI interface supports mode 3 slave operation. The relationship between SPI\_SCK, SPI\_MOSI and SPI\_MISO is illustrated in Figure 18. Data on SPI\_MOSI is sampled on the rising edge of SPI\_SCK. The SA2443A can be programmed (by firmware running on the SA2443A microcontroller) to transition SPI\_MISO on either the falling edge or rising edge of SPI\_SCK.

Care should be taken that none of the SPI interface signals are driven HIGH when  $V_{DDA}$  is lower than the minimum recommended operating voltage; see <u>Table 66</u>.

The write register command and all initialization packets are always sent MSB first. The bit order of the read register data, DMA size and DMA data packets can be programmed (by firmware running on the SA2443A microcontroller) to allow either the LSB or the MSB in a packet to be transferred first.

#### 10.14.2 Mailboxes and scratch registers

The SPI2 interface contains 8 mailboxes: 4 local mailboxes (SPI2\_LOC\_MB0 to SPI2\_LOC\_MB3; see <u>Table 20</u>) and 4 host mailboxes (SPI2\_HST\_MB0 to SPI2\_HST\_MB3; see <u>Table 22</u>).

The local mailboxes are written to by the host and read from by the SA2443A microcontroller. A local SPI2 interrupt is generated when the host writes to one of the local mailboxes. The enabling of generation of the interrupt is programmable.

The host mailboxes are written to by the SA2443A microcontroller and read from by the host. A host interrupt is signaled on the SPI\_EXT\_INT pin when the microcontroller writes to one of the host mailboxes.

Eight scratch registers are provided: 4 local registers (SPI2\_LOC\_SR0 to SPI2\_LOC\_SR3; see <u>Table 21</u>) and 4 host registers (SPI2\_HST\_SR0 to SPI2\_HST\_SR3; see <u>Table 23</u>). The scratch registers are accessed in the same way as the mailbox registers, the only difference being that no interrupts are generated when the scratch registers are written.

#### 10.14.3 DMA controller

The DMA controller provides efficient transfer of data between the host and SA2443A internal memory. The host initiates all DMA transfers.

The DMA controller supports data transfers from 0 bytes to 65535 bytes.

# 10.14.4 Host SPI operations

The host can read or write registers in the SPI2 interface and initiate DMA transfers.

#### 10.14.4.1 Write register command

The write register command is used by the host to write data into SPI interface registers. It consists of one 16-bit packet. The command format is shown in Table 7.

Table 7. Write register command packet

| Bit      | Symbol        | Value      | Description                               |

|----------|---------------|------------|-------------------------------------------|

| 15       | COMMAND_TYPE  | 1h         | indicates a host-to-slave transfer        |

| 14 to 10 | REG_ADDR[4:0] | 00h to 1Ah | see Table 16 for valid register addresses |

| 9 and 8  | -             | -          | reserved                                  |

| 7 to 0   | REG_DATA[7:0] | 00h to FFh | register data                             |

# 10.14.4.2 Read register command

The read register command sequence is used by the host to read data from SPI interface registers and consists of two packets:

- Read register initialization packet (16-bit, host-to-slave). The format of this packet is shown in <u>Table 8</u>.

- Read data package (16-bit, slave-to-host). The format of this packet is shown in Table 9.

Table 8. Read register command initialization packet

| Bit      | Symbol        | Value      | Description                               |

|----------|---------------|------------|-------------------------------------------|

| 15       | COMMAND_TYPE  | 0h         | indicates a slave-to-host transfer        |

| 14 to 10 | REG_ADDR[4:0] | 00h to 1Ah | see Table 16 for valid register addresses |

| 9 to 0   | -             | -          | reserved                                  |

Table 9. Read register command data packet

|         |               | •          |               |

|---------|---------------|------------|---------------|

| Bit     | Symbol        | Value      | Description   |

| 15 to 8 | -             | -          | reserved      |

| 7 to 0  | REG_DATA[7:0] | 00h to FFh | register data |

BGW200EG\_1 © NXP B.V. 2007. All rights reserved.

#### 10.14.4.3 Host-to-slave DMA transfer

The host-to-slave DMA command sequence is used to transfer data from the host into internal memory in the SA2443A and consists of the following packets:

- DMA initialization packet (16-bit, host-to-slave); see Table 10.

- DMA length packet (16-bit, host-to-slave); see Table 11.

- DMA data packets (8-bit, host-to-slave); see Table 12.

# Table 10. Host-to-slave DMA initialization packet

| Bit      | Symbol         | Value | Description                        |

|----------|----------------|-------|------------------------------------|

| 15       | COMMAND_TYPE   | 1h    | indicates a host-to-slave transfer |

| 14 to 10 | INIT_CODE[4:0] | 03h   | host-to-slave DMA initialization   |

| 9 to 0   | -              | -     | reserved                           |

#### Table 11. Host-to-slave DMA length packet

| Bit     | Symbol         | Value          | Description                       |

|---------|----------------|----------------|-----------------------------------|

| 15 to 0 | DATA_LEN[15:0] | 0000h to FFFFh | number of bytes to be transferred |

### Table 12. Host-to-slave DMA data packet

| Bit    | Symbol    | Value      | Description |

|--------|-----------|------------|-------------|

| 7 to 0 | DATA[7:0] | 00h to FFh | DMA data    |

# 10.14.4.4 Slave-to-host DMA command sequence

The slave-to-host DMA command sequence is used to transfer data from SA2443A internal memory to the host and consists of the following packets:

- DMA initialization packet (16-bit, slave-to-host); see Table 13.

- DMA length packet (16-bit, slave-to-host); see Table 14.

- DMA data packets (8-bit, slave-to-host); see Table 15.

### Table 13. Slave-to-host DMA initialization packet

| Bit      | Symbol         | Value | Description                        |

|----------|----------------|-------|------------------------------------|

| 15       | COMMAND_TYPE   | 0h    | indicates a slave-to-host transfer |

| 14 to 10 | INIT_CODE[4:0] | 04h   | slave-to-host DMA initialization   |

| 9 to 0   | -              | -     | reserved                           |

# Table 14. Slave-to-host DMA length packet

| Bit     | Symbol         | Value          | Description                       |

|---------|----------------|----------------|-----------------------------------|

| 15 to 0 | DATA_LEN[15:0] | 0000h to FFFFh | number of bytes to be transferred |

#### Table 15. Slave-to-host DMA data packet

| Bit    | Symbol    | Value      | Description |

|--------|-----------|------------|-------------|

| 7 to 0 | DATA[7:0] | 00h to FFh | DMA data    |

# 10.14.5 SPI2 registers

# 10.14.5.1 Register overview

Table 16. SPI2 registers

| Register      | Address | Access |      | Description                                | Reference |

|---------------|---------|--------|------|--------------------------------------------|-----------|

|               |         | Local  | Host |                                            |           |

| SPI2_LOC_ISCR | 00h     | R/W    | R    | local mailbox interrupt status and control | Table 17  |

| SPI2_HST_ISCR | 01h     | R      | R/W  | host mailbox interrupt status and control  | Table 18  |

| SPI2_DMA_SCR  | 02h     | R/W    | R    | DMA status and control register            | Table 19  |

| SPI2_LOC_MB0  | 05h     | R      | R/W  | local mailbox 0 (host-to-slave)            | Table 20  |

| SPI2_LOC_MB1  | 06h     | R      | R/W  | local mailbox 1 (host-to-slave)            |           |

| SPI2_LOC_MB2  | 07h     | R      | R/W  | local mailbox 2 (host-to-slave)            |           |

| SPI2_LOC_MB3  | 08h     | R      | R/W  | local mailbox 3 (host-to-slave)            |           |

| SPI2_LOC_SR0  | 0Ah     | R      | R/W  | local scratch register 0 (host-to-slave)   | Table 21  |

| SPI2_LOC_SR1  | 0Bh     | R      | R/W  | local scratch register 1 (host-to-slave)   |           |

| SPI2_LOC_SR2  | 0Ch     | R      | R/W  | local scratch register 2 (host-to-slave)   |           |

| SPI2_LOC_SR3  | 0Dh     | R      | R/W  | local scratch register 3 (host-to-slave)   |           |

| SPI2_HST_MB0  | 0Fh     | R/W    | R    | host mailbox 0 (slave-to-host)             | Table 22  |

| SPI2_HST_MB1  | 10h     | R/W    | R    | host mailbox 1 (slave-to-host)             |           |

| SPI2_HST_MB2  | 11h     | R/W    | R    | host mailbox 2 (slave-to-host)             |           |

| SPI2_HST_MB3  | 12h     | R/W    | R    | host mailbox 3 (slave-to-host)             |           |

| SPI2_HST_SR0  | 14h     | R/W    | R    | host scratch register 0 (slave-to-host)    | Table 23  |

| SPI2_HST_SR1  | 15h     | R/W    | R    | host scratch register 1 (slave-to-host)    |           |

| SPI2_HST_SR2  | 16h     | R/W    | R    | host scratch register 2 (slave-to-host)    |           |

| SPI2_HST_SR3  | 17h     | R/W    | R    | host scratch register 3 (slave-to-host)    |           |

| SPI2_RST_CR   | 19h     | R/W    | R/W  | reset control register                     | Table 24  |

| SPI2_DMA_ISCR | 1Ah     | R/W    | R    | DMA interrupt status and control           | Table 25  |

# 10.14.5.2 Register details

Table 17. SPI2\_LOC\_ISCR register - SPI2 local mailbox interrupt status and control (00h)

Legend: \* reset value

| Bit | Symbol          | Access |      | Value | Description                                            |

|-----|-----------------|--------|------|-------|--------------------------------------------------------|

|     |                 | Local  | Host |       |                                                        |

| 7   | LMB3_INT_EN     | R/W    | R    |       | local mailbox 3 interrupt control                      |

|     |                 |        |      | 0*    | do not generate interrupt when mailbox is written      |

|     |                 |        |      | 1     | generate interrupt when mailbox is written by the host |

| 6   | LMB2_INT_EN     | R/W    | R    |       | local mailbox 2 interrupt control                      |

|     |                 |        |      | 0*    | do not generate interrupt when mailbox is written      |

|     |                 |        |      | 1     | generate interrupt when mailbox is written by the host |

| 5   | LMB1_INT_EN R/W | R/W    | R    |       | local mailbox 1 interrupt control                      |

|     |                 |        |      | 0*    | do not generate interrupt when mailbox is written      |

|     |                 |        |      | 1     | generate interrupt when mailbox is written by the host |

IEEE 802.11b System-in-Package

Table 17. SPI2\_LOC\_ISCR register - SPI2 local mailbox interrupt status and control (00h) ...continued Legend: \* reset value

| Bit | Symbol        | Access | Access |    | Description                                            |

|-----|---------------|--------|--------|----|--------------------------------------------------------|

|     |               | Local  | Host   |    |                                                        |

| 4   | LMB0_INT_EN   | R/W    | R      | •  | local mailbox 0 interrupt control                      |

|     |               |        |        | 0* | do not generate interrupt when mailbox is written      |

|     |               |        |        | 1  | generate interrupt when mailbox is written by the host |

| 3   | LMB3_INT_STAT | R/W[1] | R      |    | local mailbox 3 interrupt status                       |

|     |               |        |        | 0* | no interrupt pending                                   |

|     |               |        |        | 1  | mailbox 3 interrupt pending                            |

| 2   | LMB2_INT_STAT | R/W[1] | R      |    | local mailbox 2 interrupt status                       |

|     |               |        |        | 0* | no interrupt pending                                   |

|     |               |        |        | 1  | mailbox 2 interrupt pending                            |

| 1   | LMB1_INT_STAT | R/W[1] | R      |    | local mailbox 1 interrupt status                       |

|     |               |        |        | 0* | no interrupt pending                                   |

|     |               |        |        | 1  | mailbox 1 interrupt pending                            |

| 0   | LMB0_INT_STAT | R/W[1] | R      |    | local mailbox 0 interrupt status                       |

|     |               |        |        | 0* | no interrupt pending                                   |

|     |               |        |        | 1  | mailbox 0 interrupt pending                            |

<sup>[1]</sup> This bit will be cleared following a local read.

Table 18. SPI2\_HST\_ISCR register - SPI2 host mailbox interrupt status and control (01h) Legend: \* reset value

| Bit | Symbol        | Access |        | Value | Description                                             |

|-----|---------------|--------|--------|-------|---------------------------------------------------------|

|     |               | Local  | Host   |       |                                                         |

| 7   | HMB3_INT_EN   | R      | R/W    |       | host mailbox 3 interrupt control                        |

|     |               |        |        | 0*    | do not generate interrupt when mailbox is written       |

|     |               |        |        | 1     | generate interrupt when mailbox is written by the slave |

| 6   | HMB2_INT_EN   | R      | R/W    |       | host mailbox 2 interrupt control                        |

|     |               |        |        | 0*    | do not generate interrupt when mailbox is written       |

|     |               |        |        | 1     | generate interrupt when mailbox is written by the slave |

| 5   | HMB1_INT_EN   | R      | R/W    |       | host mailbox 1 interrupt control                        |

|     |               |        |        | 0*    | do not generate interrupt when mailbox is written       |

|     |               |        |        | 1     | generate interrupt when mailbox is written by the slave |

| 4   | HMB0_INT_EN   | R      | R/W    |       | host mailbox 0 interrupt control                        |

|     |               |        |        | 0*    | do not generate interrupt when mailbox is written       |

|     |               |        |        | 1     | generate interrupt when mailbox is written by the slave |

| 3   | HMB3_INT_STAT | R      | R/W[1] |       | host mailbox 3 interrupt status                         |

|     |               |        |        | 0*    | no interrupt pending                                    |

|     |               |        |        | 1     | mailbox 3 interrupt pending                             |

| 2   | HMB2_INT_STAT | TAT R  | R/W[1] |       | host mailbox 2 interrupt status                         |

|     |               |        |        | 0*    | no interrupt pending                                    |

|     |               |        |        | 1     | mailbox 2 interrupt pending                             |

Table 18. SPI2\_HST\_ISCR register - SPI2 host mailbox interrupt status and control (01h) ...continued Legend: \* reset value

| Bit | Symbol        | Access |        | Value | Description                     |

|-----|---------------|--------|--------|-------|---------------------------------|

|     |               | Local  | Host   |       |                                 |

| 1   | HMB1_INT_STAT | R      | R/W[1] |       | host mailbox 1 interrupt status |

|     |               |        |        | 0*    | no interrupt pending            |

|     |               |        |        | 1     | mailbox 1 interrupt pending     |

| 0   | HMB0_INT_STAT | R      | R/W[1] |       | host mailbox 0 interrupt status |

|     |               |        |        | 0*    | no interrupt pending            |

|     |               |        |        | 1     | mailbox 0 interrupt pending     |

<sup>[1]</sup> This bit will be cleared following a host read.

Table 19. SPI2\_DMA\_SCR register - SPI2 DMA status and control (02h)

Legend: \* reset value

| Bit | Symbol        | Access | Access |    | Description                                            |

|-----|---------------|--------|--------|----|--------------------------------------------------------|

|     |               | Local  | Host   |    |                                                        |

| 7   | S2H_DMA1_STAT | R      | R      |    | slave-to-host DMA channel 1 status                     |

|     |               |        |        | 0* | DMA idle                                               |

|     |               |        |        | 1  | DMA transfer is ongoing                                |

| 6   | S2H_DMA0_STAT | R      | R      |    | slave-to-host DMA channel 0 status                     |

|     |               |        |        | 0* | DMA idle                                               |

|     |               |        |        | 1  | DMA transfer is ongoing                                |

| 5   | H2S_DMA1_STAT | R      | R      |    | host-to-slave DMA channel 1 status                     |

|     |               |        |        | 0* | DMA idle                                               |

|     |               |        |        | 1  | DMA transfer is ongoing                                |

| 4   | H2S_DMA0_STAT | R      | R      |    | host-to-slave DMA channel 0 status                     |

|     |               |        |        | 0* | DMA idle                                               |

|     |               |        |        | 1  | DMA transfer is ongoing                                |

| 3   | S2H_DMA_PEND1 | R/W    | R      |    | slave-to-host DMA channel 1 data pending status        |

|     |               |        |        | 0* | no data pending                                        |

|     |               |        |        | 1  | data pending                                           |

| 2   | S2H_DMA_PEND0 | R/W    | R      |    | slave-to-host DMA channel 0 data pending status        |

|     |               |        |        | 0* | no data pending                                        |

|     |               |        |        | 1  | data pending                                           |

| 1   | NEXT_S2H_CHAN | R/W    | R      |    | DMA channel to be used for next slave-to-host transfer |

|     |               |        |        | 0* | TX DMA channel 0 will be used                          |

|     |               |        |        | 1  | TX DMA channel 1 will be used                          |

| 0   | NEXT_H2S_CHAN | R/W    | R      |    | DMA channel to be used for next host-to-slave transfer |

|     |               |        |        | 0* | RX DMA channel 0 will be used                          |

|     |               |        |        | 1  | RX DMA channel 1 will be used                          |

Table 20. SPI2\_LOC\_MBn[1] register - SPI2 local mailbox n (05h to 08h)

Legend: \* reset value

| Bit    | Symbol         | Access |        | Value | Description  |

|--------|----------------|--------|--------|-------|--------------|

|        |                | Local  | Host   |       |              |

| 7 to 0 | MBOX_DATA[7:0] | R      | R/W[2] | 00h*  | mailbox data |

<sup>[1]</sup> Register definition is the same for all local mailboxes; replace n with the mailbox number (0 to 3).

### Table 21. SPI2\_LOC\_SRn[1] register - SPI2 local scratch register n (0Ah to 0Dh)

Legend: \* reset value

| Bit    | Symbol          | Access |      | Value | Description  |

|--------|-----------------|--------|------|-------|--------------|

|        |                 | Local  | Host |       |              |

| 7 to 0 | SCRCH_DATA[7:0] | R      | R/W  | 00h*  | scratch data |

<sup>[1]</sup> Register definition is the same for all local scratch registers; replace n with the scratch register number (0 to 3).

### Table 22. SPI2\_HST\_MBn[1] register - SPI2 host mailbox n (Fh to 12h)

Legend: \* reset value

| Bit    | Symbol         | Access |      | Value | Description  |

|--------|----------------|--------|------|-------|--------------|

|        |                | Local  | Host |       |              |

| 7 to 0 | MBOX_DATA[7:0] | R/W[2] | R    | 00h*  | mailbox data |

<sup>[1]</sup> Register definition is the same for all host mailboxes; replace n with the mailbox number (0 to 3).

### Table 23. SPI2\_HST\_SRn[1] register - SPI2 host scratch register n (14h to 17h)

Legend: \* reset value

| Bit    | Symbol          | Access |      | Value | Description  |

|--------|-----------------|--------|------|-------|--------------|

|        |                 | Local  | Host |       |              |

| 7 to 0 | SCRCH_DATA[7:0] | R/W    | R    | 00h*  | scratch data |

<sup>[1]</sup> Register definition is the same for all host scratch registers; replace n with the scratch register number (0 to 3).

### Table 24. SPI2\_RST\_CR register - SPI2 reset control (19h)

Legend: \* reset value

| Bit    | Symbol         | Access |      | Value | Description                             |

|--------|----------------|--------|------|-------|-----------------------------------------|

|        |                | Local  | Host |       |                                         |

| 7 to 3 | -              | R      | R    | 00h*  | reserved                                |

| 2      | SPI2_HOST_RST  | R/W    | R    |       | SPI2 interface host side reset status   |

|        |                |        |      | 0*    | SPI2 interface host side operational    |

|        |                |        |      | 1     | SPI2 interface host side reset ongoing  |

| 1      | SPI2_SLAVE_RST | R/W    | R    |       | SPI2 interface slave side reset status  |

|        |                |        |      | 0*    | SPI2 interface slave side operational   |

|        |                |        |      | 1     | SPI2 interface slave side reset ongoing |

BGW200EG\_1 © NXP B.V. 2007. All rights reserved.

<sup>[2]</sup> Writing to this register generates an interrupt to the local microcontroller if bit LMBn\_INT\_EN is set in register SPI2\_LOC\_ISCR (see Table 17). A local read clears the interrupt.

<sup>[2]</sup> Writing to this register generates an interrupt to the SPI host if bit HMBn\_INT\_EN is set in register SPI2\_HST\_ISCR; see <u>Table 18</u>. A host read clears the interrupt.

IEEE 802.11b System-in-Package

Table 24. SPI2\_RST\_CR register - SPI2 reset control (19h) ...continued

Legend: \* reset value

| Bit | Symbol      | Access |      | Value | Description           |

|-----|-------------|--------|------|-------|-----------------------|

|     |             | Local  | Host |       |                       |

| 0   | RST_SA2443A | R      | R/W  |       | SA2443A reset control |

|     |             |        |      | 0*    | do not reset SA2443A  |

|     |             |        |      | 1     | reset SA2443A[1]      |

<sup>[1]</sup> A host write to this bit will result in the SA2443A being reset.

Table 25. SPI2\_DMA\_ISCR register - SPI2 DMA interrupt status and control (1Ah)

Legend: \* reset value

| Bit | Symbol        | Access |      | Value | Description                                        |

|-----|---------------|--------|------|-------|----------------------------------------------------|

|     |               | Local  | Host |       |                                                    |