## 5.5V-100V Wide Input Voltage Range Synchronous Buck Controller

#### **FEATURES**

- Synchronous DCDC Buck Controller

- 5.5V-100V Wide Input Range

- 0.8V-60V Adjustable Output Voltage

- 0.8V±1% Reference Voltage

- 40ns Minimum ton for low duty ratio

- 150ns Minimum toff for high duty ratio

- 100 KHz to 1.2 MHz Switching Frequency

- Clock Synchronization In/Out capability

- Selectable Diode Emulation or FPWM

- Frequency Spread Spectrum Modulation

- 7.5-V Gate Drivers

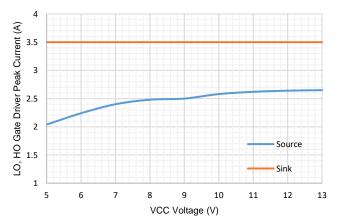

- 2.3-A Source and 3.5-A Sink Current

- Low-side Soft Start for prebiased Start-up

- Fast Line and Load Transient Response

- Voltage-mode control with line feedforward

- High Gain Bandwidth Error Amplifier

- Protection Features for Robustness

- Adjustable Soft Start time

- Hiccup-mode Overcurrent Protection

- Input UVLO with hysteresis

- VCC and Gate-drive UVLO Protection

- Precision Enable Input Threshold

- Open-drain Power Good Indicator

- Over Temperature Shutdown Protection

- External VCC Input for Bypassing Internal LDO

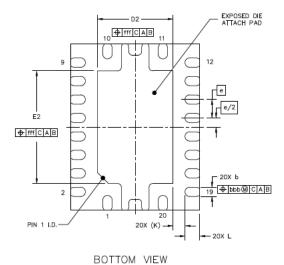

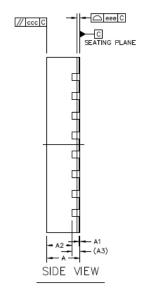

- Available in QFN-20L 3.5mmx4.5mm Package

#### **APPLICATIONS**

- High Current Distributed Power Systems

- Telecom, Datacom

- Non-isolated PoE and IP Camera

- Industrial Motor Control

- High Power Automotive DCDC

#### **DESCRIPTION**

The SCT82A30 is a 100V voltage mode control synchronous buck controller with line feed forward. 40ns minimum on-time of controlled high side MOSFET supports high conversion ratio, enabling the direct stepdown conversion from a 48V input to low-voltage rail reducing system complexity and solution cost. The device operates at nearly 100% duty cycle if needed during input voltage drops as low as 6V.

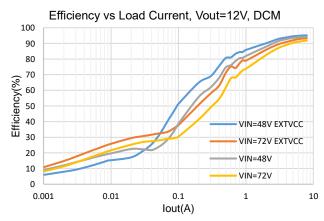

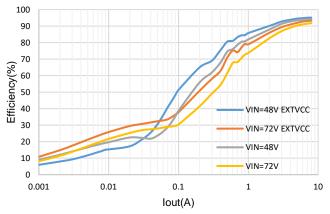

The SCT82A30 support Forced-PWM (FPWM) and Diode Emulation Mode. FPWM operation eliminates switching frequency variation to minimize EMI, while user selectable diode emulation lowers current consumption at light-load condition. The adjustable switching frequency as high as 1.2MHz can be synchronized to an external clock source to eliminate beat frequencies in noise sensitive applications.

An external voltage or the output of the buck converter itself source can power internal VCC or EXTVCC helping to increase overall efficiency and decrease internal self-heating from power dissipated in the internal VCC LDO even with 5V output voltage.

The SCT82A30 features additional features for flexible and robust design including a configurable soft start, an open-drain power-good monitor for fault reporting and output monitoring, monotonic start-up into pre-biased loads, integrated VCC bias supply regulator and bootstrap diode, external power supply tracking, precision enable input with hysteresis for adjustable line under voltage lockout (UVLO), hiccup-mode overload protection, and thermal shutdown protection with automatic recovery.

The device is available in a low-profile package QFN-20L 3.5mmx4.5mm with enhanced thermal power pad.

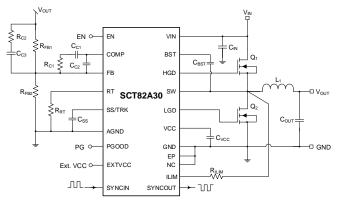

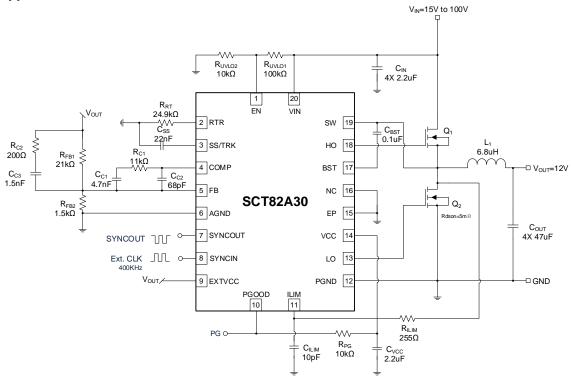

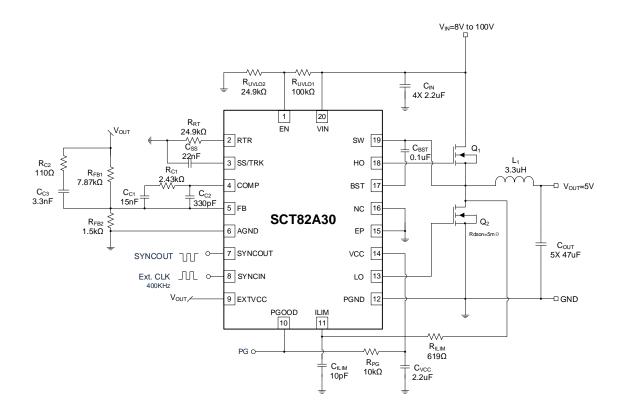

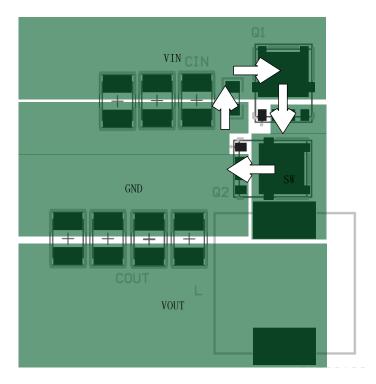

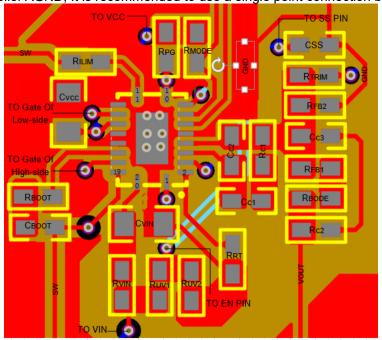

#### TYPICAL APPLICATION

For more information www.silicontent.com © 2022 Silicon Content Technology Co., Ltd. All Rights Reserved 1

#### **REVISION HISTORY**

Revision 1.0: Released to Market

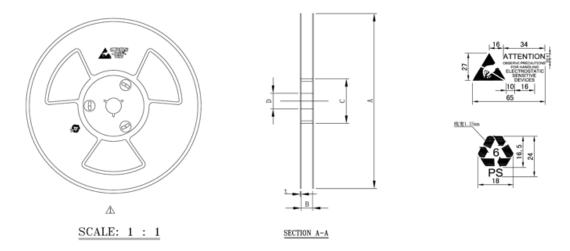

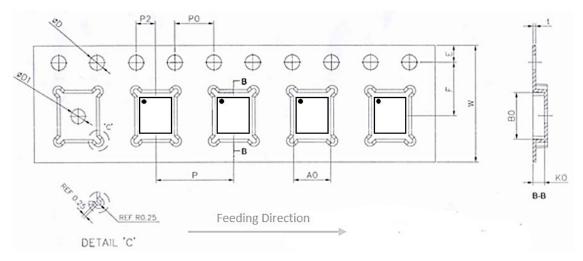

#### **DEVICE ORDER INFORMATION**

| PART NUMBER | PACKAGE MARKING | PACKAGE DISCRIPTION |

|-------------|-----------------|---------------------|

| SCT82A30DHK | 2A30            | QFN-20L 4.5mmX3.5mm |

<sup>1)</sup> For Tape & Reel, Add Suffix R (e.g. SCT82A30DHKR)

#### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature unless otherwise noted<sup>(1)</sup>

| DESCRIPTION                          | MIN  | MAX | UNIT |

|--------------------------------------|------|-----|------|

| VIN                                  | -0.3 | 105 | V    |

| SW                                   | -1   | 105 | V    |

| SW (20ns transient)                  | -5   | 105 | V    |

| ILIM                                 | -1   | 105 | V    |

| EN                                   | -0.3 | 105 | V    |

| VCC, EXTVCC,LO                       | -0.3 | 14  | V    |

| FB, COMP, SS/TRK, RT                 | -0.3 | 6   | V    |

| SYNCIN                               | -0.3 | 14  | V    |

| BST                                  | -0.3 | 115 | V    |

| BST to VCC                           |      | 105 | V    |

| BST to SW                            | -0.3 | 14  | V    |

| VCC to BST (20ns transient)          |      | 7   | V    |

| LO (20ns transient)                  | -3   |     | V    |

| PGOOD                                | -0.3 | 14  | V    |

| Junction temperature                 | -40  | 150 | °C   |

| Storage temperature T <sub>STG</sub> | -65  | 150 | °C   |

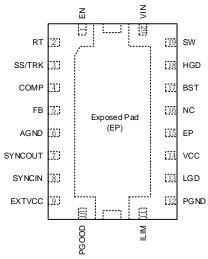

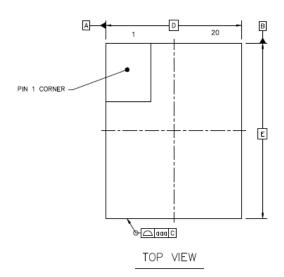

## **PIN CONFIGURATION**

Top View: 20-Lead Plastic QFN 3.5mmx4.5mm

#### **PIN FUNCTIONS**

| NAME | NO. | I/O <sup>(1)</sup> | PIN FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|-----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN   | 1   | I                  | Enable input and under voltage lockout programming pin. If the EN voltage is below 0.4 V, the controller is in the shutdown mode with all functions disabled. If the EN voltage is greater than 0.4 V and less than 1.2 V, the regulator is in standby mode with the VCC regulator operating, the SS pin grounded, and no switching at the HGD and LGD outputs. If the EN voltage is above 1.2V, the SS/TRK voltage can ramp and pulse-width modulated gate-drive signals are delivered to the HGD and LGD pins. The user can use EN pin program input under voltage lockout UVLO threshold. A 10μA current source is enabled when EN exceeds 1.2 V and flows through the external UVLO programing resistor divider to provide hysteresis. Hysteresis can be adjusted by varying the resistance of the external divider. |

| RT   | 2   | I                  | Oscillator frequency adjust pin. The internal oscillator frequency is programmed with a single resistor between RT and the AGND. Programmed oscillator frequency is 100KHz to 1.2MHz. An RT pin resistor is required even when using the SYNCIN pin to synchronize to an external clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

For more information www.silicontent.com © 2022 Silicon Content Technology Co., Ltd. All Rights Reserved

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause device permanent damage. The device is not guaranteed to function outside of its Recommended Operation Conditions.

<sup>(2)</sup> The IC includes over temperature protection to protect the device during overload conditions. Junction temperature will exceed 170°C when over temperature protection is active. Continuous operation above the specified maximum operating junction temperature will reduce lifetime.

| SS/TRK  | 3  | I | Soft-start and voltage-tracking pin. An internal 10µA current source charges an external capacitor to set the ramp rate of the error amplifier reference during start-up. When the SS/TRK pin voltage is less than 0.8 V, the SS/TRK voltage is noninverting input of the error amp. When the SS/TRK voltage exceeds 0.8 V, the noninverting of amplifier is controlled by the internal 0.8-V reference. SS/TRK is discharged to ground during standby and fault conditions. After start-up, the SS/TRK voltage is clamped at 115 mV above the FB pin voltage. If FB falls due to a load fault, SS/TRK is discharged to a level 115 mV above FB to provide a controlled recovery when the fault is removed. Voltage tracking can be implemented by connecting a low impedance reference between 0 V and 0.8 V to the SS/TRK pin. The 10µA SS/TRK charging current flows into the reference and produces a voltage error if the impedance is not sufficiently low. Connect a minimum capacitance 2.2nF from SS/TRK to AGND. |

|---------|----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMP    | 4  | 0 | Low impedance output of the internal error amplifier. Connect the loop compensation network between the COMP pin and the FB pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FB      | 5  | I | Feedback connection to the inverting input of the internal error amplifier. A resistor divider from the output to this pin sets the output voltage regulation level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AGND    | 6  | Р | Analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

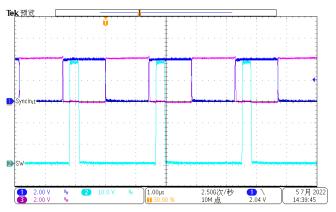

| SYNCOUT | 7  | 0 | Synchronization output. Logic output that provides a clock signal that is 180° out-of-phase with the high-side FET gate drive. Connect SYNCOUT of the master SCT82A30 to the SYNCIN pin of a second SCT82A30 to operate two controllers at the same frequency with 180° interleaved high-side FET switch turn-on transitions. Note that the SYNCOUT pin does not provide 180° interleaving when the controller is operating from an external clock that is different from the free-running frequency set by the RT resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SYNCIN  | 8  | I | Dual function pin for providing an optional clock input and for enabling diode emulation by the low-side MOSFET. Connecting a clock signal to the SYNCIN pin synchronizes switching to the external clock. Diode emulation by the low-side MOSFET is disabled when the controller is synchronized to an external clock, and negative inductor current can flow in the low-side MOSFET with light loads. A continuous logic low state at the SYNCIN pin enables diode emulation to prevent reverse current flow in the inductor. Diode emulation results in discontinuous mode operation (DCM) at light loads, which improves efficiency. A logic high state at the SYNCIN pin disables diode emulation producing forced-PWM (FPWM) operation. During soft-start when SYNCIN is high or a clock signal is present, the SCT82A30 operates in diode emulation mode until the output is in regulation, then gradually increases the SW zero-cross threshold, resulting in a gradual transition from DCM to FPWM.               |

| EXTVCC  | 9  | I | External VCC Input. When EXTVCC exceeds 4.6V, an internal switch connects this pin to internal VCC and shuts down the internal regulator so that the controller and gate drive power is drawn from EXTVCC. EXTVCC should not exceed 14V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PGOOD   | 10 | 0 | Power Good indicator. This pin is an open-drain output. A high state indicates that the voltage at the FB pin is within a specified tolerance window centered at 0.8 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ILIM    | 11 | ı | Current limit and current sense comparator input. A current sourced from the ILIM pin through an external resistor programs the threshold voltage for valley current limiting. The opposite end of the threshold adjust resistor can be connected to either the drain of the low-side MOSFET for RDS(on) sensing or to a current sense resistor connected to the source of the low-side FET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PGND    | 12 | Р | Power ground return pin for the low-side MOSFET gate driver. Connect directly to the source of the low-side MOSFET or the ground side of a shunt resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LGD     | 13 | Р | Low-side MOSFET gate drive output. Connect to the gate of the low-side synchronous rectifier FET through a short, low inductance path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## **SCT82A30**

| VCC | 14 | 0 | Output of the 7.5V bias regulator. Locally decouple to PGND using a low ESR/ESL capacitor located as close as possible to the controller. Controller bias can be supplied from an external supply that is greater than the internal VCC regulation voltage. Use caution when applying external bias to ensure that the applied voltage is not greater than the minimum VIN voltage and does not exceed the VCC pin maximum operating rating, see Recommended Operating Condition. |

|-----|----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EP  | 15 | - | Pin internally connected to exposed pad of the package. Electrically isolated.                                                                                                                                                                                                                                                                                                                                                                                                    |

| NC  | 16 | - | No electrical connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BST | 17 | 0 | Bootstrap supply for the high-side gate driver. Connect to the bootstrap (boot) capacitor. The bootstrap capacitor supplies current to the high-side FET gate and must be placed as close as possible to controller. If an external bootstrap diode is used to reduce the time required to charge the bootstrap capacitor, connect the cathode of the diode to the BST pin and anode to VCC.                                                                                      |

| HGD | 18 | Р | High-side MOSFET gate drive output. Connect to the gate of the high-side MOSFET through a short, low inductance path.                                                                                                                                                                                                                                                                                                                                                             |

| SW  | 19 | Р | Switching node of the buck controller. Connect to the bootstrap capacitor, the source terminal of the high side MOSFET and the drain terminal of the low-side MOSFET using short, low inductance paths.                                                                                                                                                                                                                                                                           |

| VIN | 20 | Р | Supply voltage input for the VCC LDO regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| EP  | -  | - | Exposed pad of the package. Electrically isolated. Solder to the system ground plane to reduce thermal resistance.                                                                                                                                                                                                                                                                                                                                                                |

<sup>(1)</sup> P=Power, G=Ground, I=Input, O=Output

#### RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range unless otherwise noted

| PARAMETER       | DEFINITION                     | MIN | MAX | UNIT |

|-----------------|--------------------------------|-----|-----|------|

| V <sub>IN</sub> | Input voltage range            | 5.5 | 100 | V    |

| VCC             | External VCC bias rail         | 8   | 13  | V    |

| EXTVCC          | External EXTVCC bias rail      | 4.8 | 13  | V    |

| TJ              | Operating junction temperature | -40 | 150 | °C   |

## **ESD RATINGS**

| PARAMETER        | DEFINITION                                                                                   | MIN  | MAX  | UNIT |

|------------------|----------------------------------------------------------------------------------------------|------|------|------|

|                  | Human Body Model(HBM), per ANSI-JEDEC-JS-001-2014 specification, all pins <sup>(1)</sup>     | -1   | +1   | kV   |

| V <sub>ESD</sub> | Charged Device Model(CDM), per ANSI-JEDEC-JS-002-2014 specification, all pins <sup>(2)</sup> | -0.5 | +0.5 | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

4 For more information www.silicontent.com © 2022 Silicon Content Technology Co., Ltd. All Rights Reserved

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

#### THERMAL INFORMATION

| PARAMETER         | THERMAL METRIC                                              | QFN-20L | UNIT |

|-------------------|-------------------------------------------------------------|---------|------|

| RθJA              | Junction to ambient thermal resistance <sup>(1)</sup>       | 37      |      |

| RθJC (top)        | Junction to case (top) thermal resistance <sup>(1)</sup>    | 28      | °C/W |

| RθJC (bot)        | Junction to case (bottom) thermal resistance <sup>(1)</sup> | 2.1     | C/VV |

| R <sub>θ</sub> ЈВ | Junction to board thermal resistance <sup>(1)</sup>         | 12      |      |

<sup>(1)</sup> SCT provides  $R_{\theta JA}$  and  $R_{\theta JC}$  numbers only as reference to estimate junction temperatures of the devices.  $R_{\theta JA}$  and  $R_{\theta JC}$  are not a characteristic of package itself, but of many other system level characteristics such as the design and layout of the printed circuit board (PCB) on which the SCT82A30 is mounted, thermal pad size, and external environmental factors. The PCB board is a heat sink that is soldered to the leads and thermal pad of the SCT82A30. Changing the design or configuration of the PCB board changes the efficiency of the heat sink and therefore the actual  $R_{\theta JC}$ .

#### **ELECTRICAL CHARACTERISTICS**

Typical values correspond to  $T_J$  = 25°C. Minimum and maximum limits apply over the -40°C to 125°C junction temperature range unless otherwise stated.  $V_{IN}$  = 48 V,  $V_{EN}$  = 1.5 V,  $R_{RT}$  = 25 k $\Omega$  unless otherwise stated.

| SYMBOL               | PARAMETER                              | TEST CONDITION                                                                    | MIN   | TYP  | MAX   | UNIT |

|----------------------|----------------------------------------|-----------------------------------------------------------------------------------|-------|------|-------|------|

| Power Sup            | ply                                    |                                                                                   |       |      |       |      |

| V <sub>IN</sub>      | Operating input voltage                |                                                                                   | 5.5   |      | 100   | V    |

| IQ_SHDN              | Shutdown input current                 | EN=0, Vcc<1V                                                                      |       | 10   |       | μΑ   |

| I <sub>Q_STBY</sub>  | Standby input current                  | EN=1V,                                                                            |       | 1.4  |       | mA   |

| IQ_OP                | Operating input current, not switching | EN=1.5V, V <sub>SS/TRK</sub> =1V                                                  |       | 1.5  |       | mA   |

| Vcc                  | VCC regulation voltage                 | V <sub>SS/TRK</sub> =0V, 9V≤V <sub>IN</sub> ≤100V,<br>0mA <i<sub>VCC≤20mA</i<sub> | 7.1   | 7.5  | 7.8   | V    |

| Vcc_uvlo             | Input UVLO Threshold                   | V <sub>IN</sub> rising                                                            |       | 4.5  |       | V    |

| VCC_0VL0             | Hysteresis                             |                                                                                   |       | 200  |       | mV   |

| Vcc_ldo              | VIN to VCC dropout voltage             | V <sub>IN</sub> =6V, V <sub>SS/TRK</sub> =0V, I <sub>VCC</sub> =20 mA             |       | 0.08 |       | V    |

| Isc_ldo              | VCC short circuit current              | Vss/trk=0V, Vcc =0V                                                               | 40    | 50   | 70    |      |

| Vextvcc              | EXTVCC switchover voltage              | V <sub>IN</sub> rising                                                            |       | 4.7  |       | V    |

| VEXTVCC              | Hysteresis                             |                                                                                   |       | 100  |       | mV   |

| Error Ampl           | ifier                                  |                                                                                   |       |      |       |      |

| V <sub>REF</sub>     | FB reference voltage                   | FB connected to COMP                                                              | 0.792 | 0.8  | 0.808 | V    |

| I <sub>FB_BIAS</sub> | FB input bias current                  | V <sub>FB</sub> =0.8V                                                             | -0.1  |      | 0.1   | uA   |

| AVOL                 | DC gain                                |                                                                                   |       | 94   |       | dB   |

| GBW                  | Unity gain bandwidth                   |                                                                                   |       | 6.5  |       | MHz  |

| ICOMP_SRC            | EA maximum source current              | V <sub>FB</sub> =V <sub>REF</sub> -100mV, V <sub>COMP</sub> =1V                   | 1000  |      |       | μΑ   |

| ICOMP_SNK            | EA maximum sink current                | V <sub>FB</sub> =V <sub>REF</sub> +100mV, V <sub>COMP</sub> =1V                   | 1000  |      |       | μA   |

| V <sub>СОМР_Н</sub>  | COMP output high voltage               | V <sub>FB</sub> =0V, COMP sourcing 1mA                                            |       | 4.5  |       | V    |

| V <sub>COMP_L</sub>  | COMP output low voltage                | COMP sinking 1mA                                                                  |       | 0.25 |       | V    |

| Enable               |                                        |                                                                                   |       |      |       |      |

|                      | Shutdown to standby EN threshold       | V <sub>EN</sub> rising                                                            |       | 0.41 |       | V    |

| V <sub>EN_SHDN</sub> | Hysteresis                             |                                                                                   |       | 30   |       | mV   |

| V <sub>EN</sub>      | Standby to operating EN threshold      | V <sub>EN</sub> rising                                                            | 1.164 | 1.2  | 1.236 | V    |

| IEN_HYS              | Standby to operating hysteresis        | V <sub>EN</sub> =1.5V                                                             | 9     | 10   | 11    | μA   |

For more information <a href="www.silicontent.com">www.silicontent.com</a> © 2022 Silicon Content Technology Co., Ltd. All Rights Reserved 5

# **SCT82A30**

| SYMBOL                  | PARAMETER                                                  | TEST CONDITION                                                        | MIN | TYP  | MAX | UNI |

|-------------------------|------------------------------------------------------------|-----------------------------------------------------------------------|-----|------|-----|-----|

| Soft-start a            | nd Voltage Tracking                                        |                                                                       |     |      |     |     |

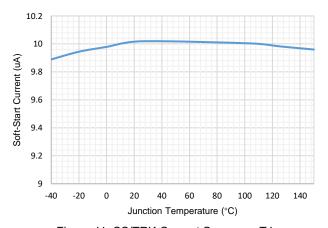

| Iss                     | SS/TRK capacitor charging current                          | Vss/TRK=0V                                                            | 8.5 | 10   | 12  | uA  |

| Rss                     | SS/TRK discharging FET resistance                          | V <sub>EN</sub> =1V, V <sub>SS/TRK</sub> =0.1V                        |     | 12   |     | Ω   |

| V <sub>SS-FB</sub>      | SS/TRK to FB offset                                        |                                                                       |     | 62   |     | mV  |

| V <sub>CC_CLAMP</sub>   | SS/TRK clamp voltage                                       | V <sub>SS/TRK</sub> – V <sub>FB</sub> , V <sub>FB</sub> =0.8V         |     | 120  |     | mV  |

| Power Goo               |                                                            |                                                                       |     |      |     |     |

| PG <sub>UTH</sub>       | PGOOD high to low - FB upper threshold                     | % of V <sub>REF</sub> , V <sub>FB</sub> rising                        | 106 | 109  | 110 | %   |

| PG <sub>U_HYS</sub>     | PGOOD upper threshold hysteresis                           | % of V <sub>REF</sub>                                                 |     | 3    |     | %   |

| PG <sub>LTH</sub>       | PGOOD high to low - FB lower threshold                     | % of V <sub>REF</sub> , V <sub>FB</sub> falling                       | 90  | 92   | 94  | %   |

| PG <sub>L_HYS</sub>     | PGOOD upper threshold hysteresis                           | % of V <sub>REF</sub>                                                 |     | 2    |     | %   |

| t <sub>PG_rising</sub>  | PGOOD rising filter                                        | FB to PGOOD rising edge                                               |     | 25   |     | us  |

| t <sub>PG_falling</sub> | PGOOD falling filter                                       | FB to PGOOD falling edge                                              |     | 25   |     | us  |

| V <sub>PG_OL</sub>      | PGOOD low state output voltage                             | V <sub>FB</sub> =0.9V, I <sub>PGOOD</sub> =2mA                        |     |      | 150 | mV  |

| I <sub>PG_OH</sub>      | PGOOD high state leakage current                           | V <sub>FB</sub> =0.8V, V <sub>PGOOD</sub> =13V                        |     |      | 100 | nA  |

| Switching I             | Frequency and External Clock Synchr                        | onization                                                             |     |      |     |     |

| Fsw <sub>1</sub>        | Switching frequency 1                                      | R <sub>RT</sub> =100 kΩ (1%)                                          |     | 100  |     | kHz |

| F <sub>SW2</sub>        | Switching frequency 2                                      | R <sub>RT</sub> =24.9 kΩ (1%)                                         |     | 400  |     | kHz |

| F <sub>SW3</sub>        | Switching frequency 3                                      | R <sub>RT</sub> =12.5 kΩ (1%)                                         |     | 780  |     | kHz |

| F <sub>RANGE_CLK</sub>  | SYNCIN external clock frequency range using                | % of nominal frequency set by RT                                      | -20 |      | 50  | %   |

| V <sub>SYNCI-IH</sub>   | Minimum SYNCIN input logic high                            |                                                                       | 1.8 |      |     | ٧   |

| Vsynci-il               | Maximum SYNCIN input logic low                             |                                                                       |     |      | 0.8 | ٧   |

| RSYNCIN                 | SYNCIN input resistance                                    | Vsyncin=3V                                                            |     | 20   |     | kΩ  |

| tsyncpw                 | SYNCIN minimum pulse width                                 | Minimum high state or low state duration                              | 50  |      |     | ns  |

| Vsynco-oh               | SYNCOUT high state output voltage                          | Isyncout=-1mA (sourcing)                                              | 3   |      |     | V   |

| Vsynco-ol               | SYNCOUT low state output voltage                           | Isyncout= 1mA (sinking)                                               |     |      | 0.4 | V   |

| tsyncout                | Delay from HGD rising to SYNCOUT leading edge              | $V_{\text{SYNCIN}}$ = 0V, $F_{\text{SW}}$ =400KHz, RT=24.9 k $\Omega$ |     | 1030 |     | ns  |

| tsyncin                 | Delay from SYNCIN leading edge to HGD rising               | 50% to 50%                                                            |     | 220  |     | ns  |

| FJITTER                 | Frequency spread spectrum in percentage of Fsw             |                                                                       |     | ±6   |     | %   |

| PWM Conti               | rol                                                        |                                                                       |     |      |     | _   |

| t <sub>ON(MIN)</sub>    | Minimum control on-time                                    | V <sub>BST</sub> -V <sub>SW</sub> =7V, HGD 50% to 50%                 |     | 40   |     | ns  |

| toff(MIN)               | Minimum control on-time                                    | V <sub>BST</sub> -V <sub>SW</sub> =7V, HGD 50% to 50%                 |     | 150  |     | ns  |

| D <sub>100</sub> K(MAX) | Maximum duty cycle                                         | Fsw=100kHz, 5V <v<sub>IN&lt;100V</v<sub>                              |     | 98   |     | %   |

| D <sub>400</sub> K(MAX) | Maximum duty cycle                                         | F <sub>SW</sub> =400kHz, 5V <v<sub>IN&lt;100V</v<sub>                 |     | 92   |     | %   |

| VRAMP(MIN)              | Ramp valley voltage (COMP at 0% duty cycle)                |                                                                       |     | 300  |     | mV  |

| K <sub>FF</sub>         | PWM feedforward gain (V <sub>IN</sub> /V <sub>RAMP</sub> ) | 5V <v<sub>IN&lt;100V</v<sub>                                          |     | 12   |     | V/V |

| Bootstrap I             | Diode and Undervoltage Threshold                           |                                                                       |     |      |     |     |

| V <sub>BST-FWD</sub>    | Diode forward voltage                                      | VCC to BST, BST sourcing 20mA                                         |     | 0.8  |     | V   |

$<sup>6 \</sup>quad \text{For more information } \underline{\text{www.silicontent.com}} \quad \textcircled{0} \text{ 2022 Silicon Content Technology Co., Ltd.} \quad \text{All Rights Reserved}$

| SYMBOL                                     | PARAMETER                                        | TEST CONDITION                                                               | MIN                       | TYP   | MAX | UNIT              |

|--------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------|---------------------------|-------|-----|-------------------|

| I <sub>Q-BST</sub>                         | BST to SW quiescent current, not switching       | V <sub>SS/TRK</sub> =0V, V <sub>SW</sub> =48V, V <sub>BST</sub> =54V         |                           | 70    |     |                   |

| $V_{BST-UV}$                               | BST to SW undervoltage detection                 | V <sub>BST</sub> -V <sub>SW</sub> falling                                    |                           | 3.4   |     | ٧                 |

| \/                                         | BST to SW undervoltage detection                 | V <sub>BST</sub> -V <sub>SW</sub> falling                                    |                           | 3.4   |     | V                 |

| V <sub>BST-UV</sub>                        | Hysteresis                                       |                                                                              |                           | 420   |     | mV                |

| Over Curre                                 | nt Protection and Valley Current Limiti          | ing                                                                          |                           |       |     |                   |

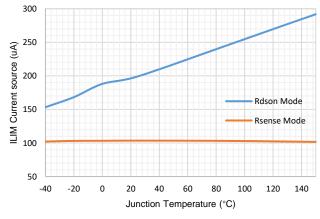

| I <sub>RS</sub>                            | ILIM source current, R <sub>SENSE</sub> mode     | Low voltage detected at ILIM                                                 | 90                        | 100   | 110 | uA                |

| I <sub>RDSON</sub>                         | ILIM source current, R <sub>DS(ON)</sub> mode    | SW voltage detected at ILIM, T <sub>J</sub> =25°C                            | 180                       | 200   | 220 | uA                |

| IRDSONTC                                   | ILIM current tempco                              | R <sub>DS-ON</sub> mode                                                      |                           | 4500  |     | ppm/ <sup>O</sup> |

| I <sub>RSTC</sub>                          | ILIM current tempco                              | R <sub>SENSE</sub> mode                                                      |                           | 0     |     | ppm/ <sup>O</sup> |

| V <sub>ILIM-TH</sub>                       | ILIM comparator threshold at ILIM                |                                                                              | -8                        | -2    | 3.5 | mV                |

| C <sub>HICC-DEL</sub>                      | Hiccup mode activation delay                     | Clock cycles with current limiting before hiccup off-time activated          |                           | 128   |     | cycles            |

| Сніссир                                    | Hiccup mode off-time after activation            | Clock cycles with no switching followed by SS/TRK release                    |                           | 16384 |     | cycles            |

| Short Circu                                | iit Protection – Duty Cycle Clamp                |                                                                              |                           |       |     |                   |

| V <sub>CLAMP-OS</sub>                      | Clamp offset voltage – no current limiting       | Clamp to COMP steady state offset voltage                                    | 0.2+V <sub>IN</sub> /75+1 |       |     | V                 |

| V <sub>CLAMP-MIN</sub>                     | Minimum clamp voltage                            | Clamp voltage with continuous current limiting                               |                           | 0     | V   |                   |

| DIODE Em                                   | ulation                                          |                                                                              |                           |       |     |                   |

| Vzcd-ss                                    | Zero crossing detect ZCD soft-start ramp         | ZCD threshold measured at SW pin 50 clock cycles after the first HGD pulse   | 0                         |       |     | mV                |

| Vzcd-dis                                   | Zero crossing detect ZCD disable threshold (CCM) | ZCD threshold measured at SW pin 1000 clock cycles after the first HGD pulse | 200                       |       |     | mV                |

| V <sub>DEM-TH</sub>                        | Diode emulation zero crossing threshold          | Measured at SW with V <sub>SW</sub> rising                                   | -15                       | -5    | 5   | mV                |

| Gate Drive                                 | r                                                |                                                                              |                           |       |     |                   |

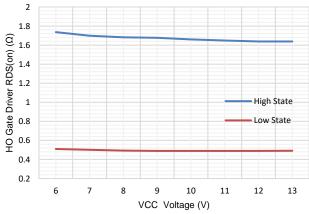

| R <sub>HGD-UP</sub>                        | HGD high state resistance, HGD to BST            | V <sub>BST</sub> –V <sub>SW</sub> =7V, I <sub>HGD</sub> =-100mA              |                           | 1.3   |     | Ω                 |

| RHGD-DOWN                                  | HGD low state resistance, HGD to SW              | V <sub>BST</sub> –V <sub>SW</sub> =7V, I <sub>HGD</sub> = 100mA              |                           | 0.6   |     | Ω                 |

| RLGD-UP                                    | LGD high state resistance, LGD to VCC            | V <sub>BST</sub> -V <sub>SW</sub> =7V, I <sub>LGD</sub> =-100mA              |                           | 1.3   |     | Ω                 |

| RLGD-DOWN                                  | LGD low state resistance, LGD to SW              | V <sub>BST</sub> -V <sub>SW</sub> =7V, I <sub>LGD</sub> = 100mA              |                           | 0.6   |     | Ω                 |

| t <sub>HGD-TR</sub><br>t <sub>LGD-TR</sub> | HGD, LGD rise times                              | V <sub>BST</sub> -V <sub>SW</sub> =7V, C <sub>LOAD</sub> =1nF, 20% to 80%    | 7                         |       |     | ns                |

| thgd-tf<br>tlgd-tf                         | HGD, LGD fall times                              | V <sub>BST</sub> -V <sub>SW</sub> =7V, C <sub>LOAD</sub> =1nF, 80% to 20%    | 4                         |       |     | ns                |

| thgd-dt                                    | HGD turn on dead time                            | V <sub>BST</sub> –V <sub>SW</sub> =7V, LGD off to HGD on. 50% to 50%         | 25                        |       |     | ns                |

| t <sub>LGD-DT</sub>                        | LGD turn on dead time                            | V <sub>BST</sub> –V <sub>SW</sub> =7V, HGD off to LGD on. 50% to 50%         | 22                        |       |     | ns                |

| Thermal Sh                                 | nutdown                                          |                                                                              |                           |       |     |                   |

|                                            | Thermal shutdown threshold                       | T <sub>J</sub> rising                                                        |                           | 175   |     | °C                |

| T <sub>SD</sub>                            |                                                  | Hysteresis                                                                   |                           | 20    |     | °C                |

For more information <a href="www.silicontent.com">www.silicontent.com</a> © 2022 Silicon Content Technology Co., Ltd. All Rights Reserved 7

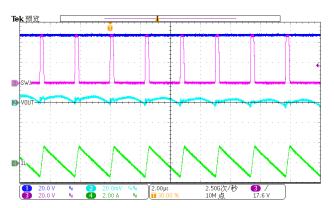

## TYPICAL CHARACTERISTICS

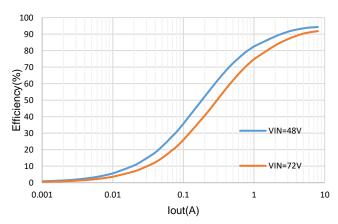

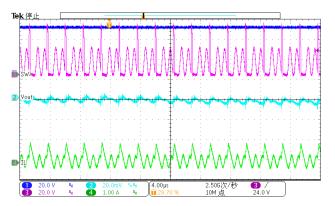

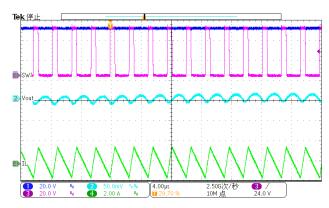

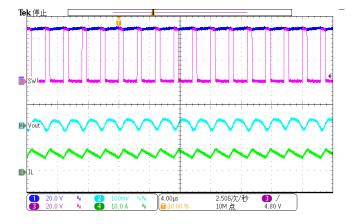

Figure 1. Efficiency vs Load Current, Vout=12V, DCM

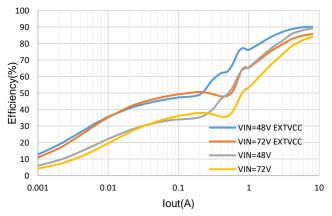

Figure 2. Efficiency vs Load Current, Vout=12V, FCCM

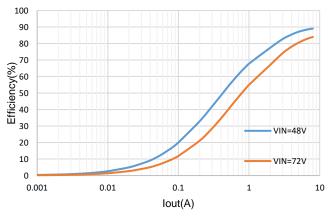

Figure 3. Efficiency vs Load Current, Vout=5V, DCM

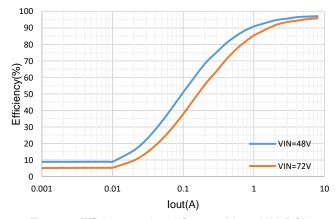

Figure 4. Efficiency vs Load Current, Vout=5V, FCCM

Figure 5. Efficiency vs Load Current, Vout=24V, DCM

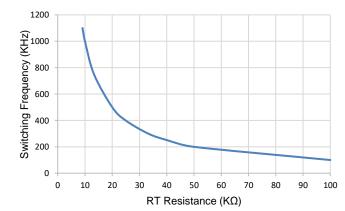

Figure 6. Oscillator Frequency vs RT Resistance

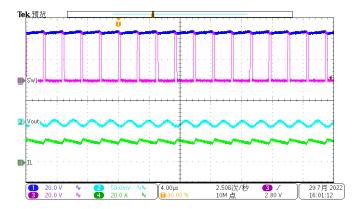

## TYPICAL CHARACTERISTICS

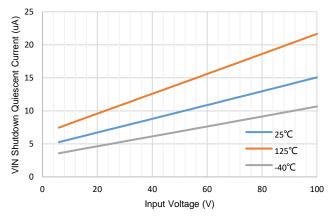

Figure 7. ISHUTDOWN vs Input Voltage

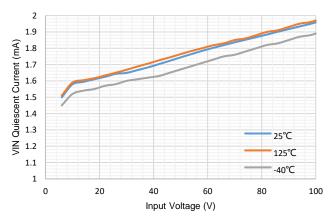

Figure 8. IQ vs Input Voltage

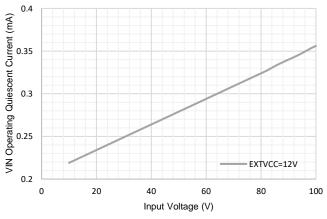

Figure 9. VIN Quiescent Current with External VCC Applied

Figure 10. ILIM Current Source vs TJ

Figure 11. SS/TRK Current Source vs TJ

Figure 12. Gate Driver Peak Current vs VCC Voltage

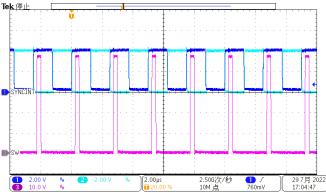

## TYPICAL CHARACTERISTICS

Figure 13. HO Driver Resistance vs VCC Voltage

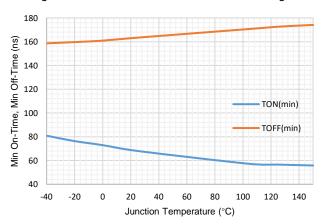

Figure 15. ton(MIN) and toff(MIN) vs TJ

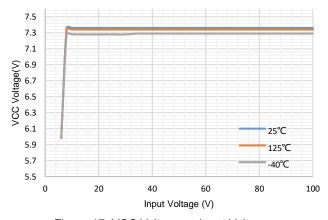

Figure 17. VCC Voltage vs Input Voltage

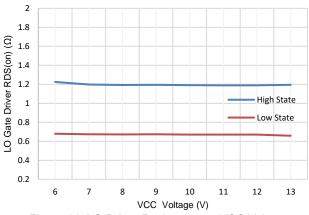

Figure 14. LO Driver Resistance vs VCC Voltage

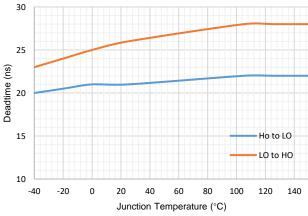

Figure 16. Deadtime vs TJ

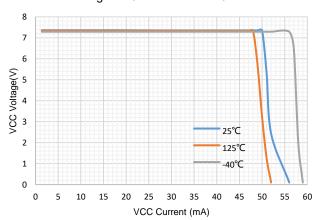

Figure 18. VCC vs ICC Characteristic

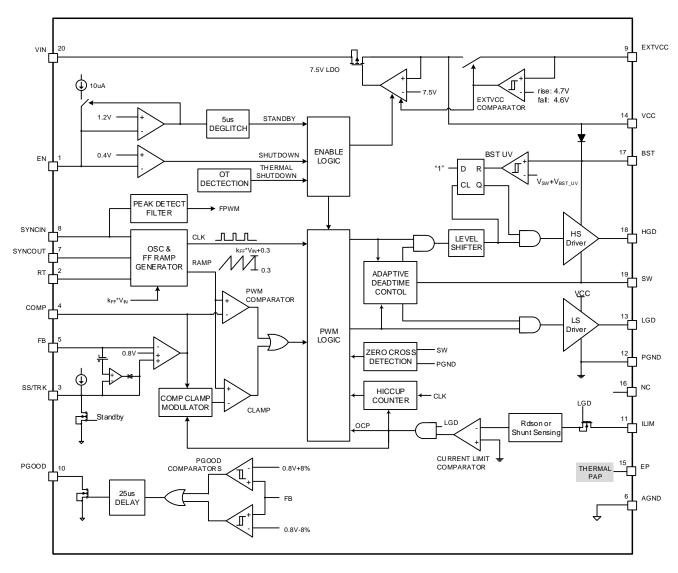

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 19. Functional Block Diagram

#### **OPERATION**

#### Overview

The SCT82A30 is a synchronous buck controller, adopting voltage mode with input feedforward, to implement a high efficiency step-down DCDC power supply for excellent line transient response over a 6V-100V wide VIN range. The output voltage range is from 0.8 V to 60 V. Voltage-mode control supports wide duty cycle range for high input/output voltage conversion ratio and low dropout applications as well. It continues to operate during input voltage drops as low as 6 V, at nearly 100% duty cycle if needed, making it an excellent choice for high performance industrial control, robotic, Datacom, and networking communication infrastructure.

The device drives external high-side and low-side NMOS power switches with robust 7.5V gate drivers suitable for standard threshold MOSFETs.

The SCT82A30 support Forced-PWM (FPWM) and Diode Emulation Mode. FPWM operation eliminates switching frequency variation to minimize EMI, while user selectable diode emulation lowers current consumption at light-load condition. The operating frequency is programmable from 100 kHz to 1.2MHz and can be synchronized to an external clock source to eliminate beat frequencies in noise-sensitive applications. The device features clock synchronization with clock input and clock output. A 180° out-of-phase clock output relative to the internal oscillator at SYNCOUT configures cascaded or multichannel power supplies to reduce input capacitor ripple current and EMI filter size.

The SCT82A30 features Frequency Spread Spectrum FSS with ±6% jittering span of the setting switching frequency and modulation rate 1/512 of switching frequency to reduce the conducted EMI.

An external voltage or the output of the buck converter itself source can power internal VCC or EXTVCC helping to increase overall efficiency and decrease internal self-heating from power dissipated in the internal VCC LDO even with 5V output voltage.

Cycle-by-cycle current limiting and over current protection can be implemented with either sensing the low-side FET RDS(on) or a current sense resistor. The SCT82A30 features additional features for flexible and robust design including a configurable soft start, an open-drain power-good monitor for fault reporting and output monitoring, monotonic start-up into pre-biased loads, integrated VCC bias supply regulator and bootstrap diode, external power supply tracking, precision enable input with hysteresis for adjustable line under voltage lockout (UVLO), hiccupmode overload protection, and thermal shutdown protection with automatic recovery.

The SCT82A30 controller is available in a 4.5-mm × 3.5-mm thermally enhanced, 20-pin QFN package

#### **Input Voltage Range**

The SCT82A30 operational input voltage range is from 6V to 100 V. The device is intended for step-down conversions from 12-V, 24-V, 48-V, 60-V, and 72-V unregulated, semi-regulated, and fully regulated supply rails. An internal LDO regulator provides a 7.5V VCC

bias rail for the gate drive and control circuits assuming the input voltage is higher than 7.5 V plus the necessary regulator dropout specification.

#### **Output Voltage Regulation Point and Accuracy**

The feedback reference voltage at the FB pin is typical 0.8 V with a feedback system accuracy over the full junction temperature range of ±1%. Junction temperature range for the device is -40°C to +125°C. the SCT82A30 is generally capable of providing output voltages in the range of 0.8 V to a maximum of 60V or slightly less than VIN depending on switching frequency and load current levels. The output voltage regulation level during normal operation is set by the feedback resistor network, RFB1 and RFB2, connected to the output and FB pin.

#### High Voltage Internal VCC Bias Supply Regulator and EXTVCC Auxiliary Supply

Power for the high side and low side MOSFET drivers and most other internal control circuitry is derived from the

VCC pin. An internal high-voltage VCC regulator directly to input voltage pin up to 100V. The output of internal VCC regulator is set up 7.5V. When the input voltage is below the VCC set point level, the VCC output tracks Vin with a small voltage drop. Connect a ceramic decoupling capacitor between 1µF and 5µF from VCC to AGND for stability.

The VCC regulator output has a current limit of 40 mA (minimum). At power up, when the VCC voltage exceeds its rising UVLO threshold of 4.5 V, the output is enabled if EN is above 1.2V, and the soft-start seguence begins. The output remains active until the VCC voltage falls below its falling UVLO threshold of typical 4.3 V or if EN goes to a standby or shutdown state.

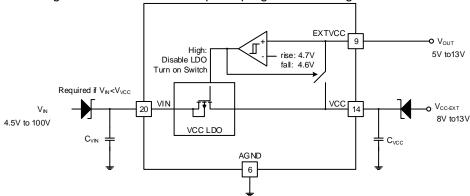

There are two ways powering the VCC pin with the external source helping to increase overall efficiency and decrease internal self-heating through power dissipated in the LDO. Connecting the output voltage or an auxiliary bias supply rail (up to 13V) to VCC using a diode. Or powering the EXTVCC pin with an external power source or from output voltage directly which is very convenient for customer especially when output voltage is setup at 5V as shown in Figure 20. If the EXTVCC pin is tied to an external source larger than 4.7V, then the internal VCC LDO is shut down and an internal switch shorts the EXTVCC pin to the VCC pin. This external power source could be the output of the buck switching converter itself if the output is programmed to higher than 4.7V.

Figure 20. VCC Bias Supply Connecting EXTVCC Auxiliary Supply

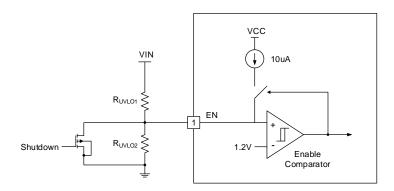

#### **Enable and programmable UVLO**

The SCT82A30 can be shut down using the EN pin. Pulling this pin below 1.2V prevents the controller from switching, and less than 0.4V1 disables most of the internal bias circuitry, including the VCC regulator. The shutdown IQ is about 7.2µA typical.

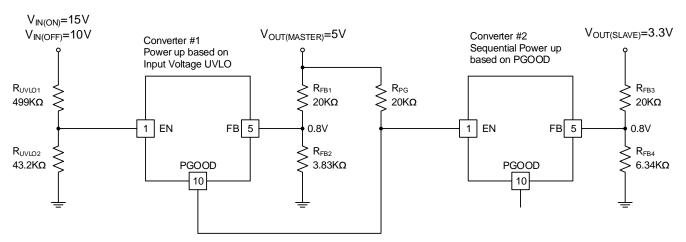

The EN input supports adjustable input under voltage lockout (UVLO) with hysteresis programmed by the resistor values for application specific power-up and power-down requirements. EN connects to a comparator-based input referenced to a 1.2V bandgap voltage. An external logic signal can be used to drive the N input to toggle the output ON and OFF and for system sequencing or protection. The simplest way to enable the operation of the SCT82A30 is to connect EN directly to VIN. This allows self-power-up of the regulator when VCC is within its valid operating range. However, many applications benefit from using a resistor divider RUVLO1 and RUVIO2 as shown in Figure 21 to establish a precision UVLO level. Use Equation 1 and Equation 2 to calculate the UVLO resistors given the required input power-up and power-down voltages.

$$R_{UVLO1} = \frac{V_{IN(ON)} - V_{IN(OFF)}}{I_{HYS}}$$

$$R_{UVLO2} = R_{UVLO1} \cdot \frac{V_{EN}}{V_{IN(ON)} - V_{EN}}$$

$$\tag{2}$$

$$R_{UVLO2} = R_{UVLO1} \cdot \frac{V_{EN}}{V_{IN(ON)} - V_{EN}} \tag{2}$$

Figure 21. Programmable Input Voltage VIN UVLO Thresholds

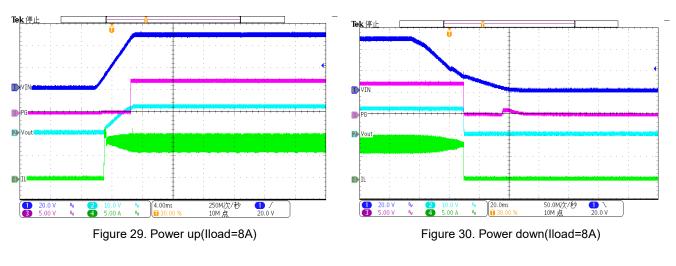

#### **Soft Start and Voltage Tracking**

The SS/TRK pin voltage controls start-up of output voltage. After the EN pin exceeds its rising threshold of 1.2 V, the SCT82A30 begins regulating the output to the level dictated by the feedback resistor network and SS/TRK voltage. A  $10\mu A$  current source charges the soft-start capacitor connecting SS/TRK pin. Soft start avoids inrush current as a result of high output capacitance to avoid an overcurrent condition. The inrush stress on the input supply rail is also reduced. The soft-start time,  $t_{SS}$ , for the output voltage to ramp to its nominal level is set by Equation 3.

$$t_{SS} = \frac{C_{SS} * V_{REF}}{I_{SS}} \tag{3}$$

where

- Css is the soft-start capacitance

- V<sub>REF</sub> is the 0.8V reference voltage

- Iss is the 10µA current sourced from the SS/TRK pin

Calculate Css using Equation 4.

$$Css [nF] = 12.5 \cdot t_{SS} [mS] \tag{4}$$

The SS/TRK pin is internally clamped to VFB + 115 mV to allow a soft-start recovery from an overload event. The clamp circuit requires a soft-start capacitance greater than 2nF for stability and has a current limit of approximately 2mA.

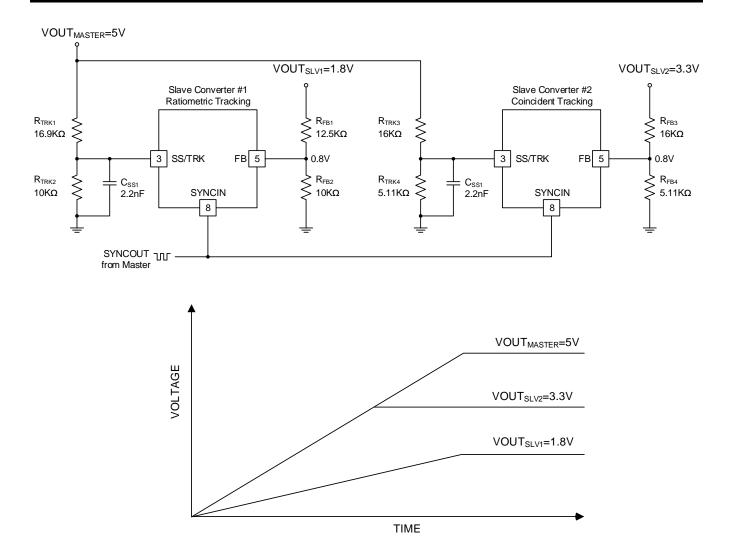

The SS/TRK pin also serves as a tracking pin when master-slave power supply tracking is required. Coincident, ratiometric, and offset tracking modes are achieved by simply dividing down the output voltage of the master with a resistor network. For coincident tracking, make the divider ratio from the external supply the same as the divider ratio for the differential feedback voltage. ratiometric tracking could be achieved by using a different ratio than the differential feedback (Figure 22). Note that the small soft-start capacitor charging current is always flowing, producing a small offset error. To minimize this error, select the tracking resistive divider values to be small enough to make this offset error negligible.

As the master voltage rises, the slave voltage rises identically (aside from the 80mV offset from SS/TRK to FB when VFB is below 0.8 V). Eventually, the slave voltage reaches its regulation voltage, at which point the internal reference takes over the regulation while the SS/TRK input continues to 115 mV above FB, and no longer controls the output voltage. In all cases, to ensure that the output voltage accuracy is not compromised by the SS/TRK voltage being too close to the 0.8V reference voltage, the final value of the SS/TRK voltage of the slave should be at least 100mV above FB.

SCI

Figure 22. Tracking Implementation with Master, Ratiometric and Coincident Slave Rails

It is the responsibility of the system designer to determine if an external soft-start capacitor is required to keep the device from entering current limit during a start-up event. Likewise, the system designer must also be aware of how fast the input supply ramps if the tracking feature is enabled.

#### **Power Good Monitor PGOOD**

The SCT82A30 provides a PGOOD indicator pin to indicate when the output voltage is within a regulation window.

When the FB voltage exceeds 94% of the internal reference VREF, the internal PGOOD switch turns off and PGOOD can be pulled high by the external pull-up. If the FB voltage falls below 92% of VREF, the internal PGOOD switch turns on, and PGOOD is pulled low to indicate that the output voltage is out of regulation.

Similarly, when the FB voltage exceeds 108% of VREF, the internal PGOOD switch turns on, pulling PGOOD low. If the FB voltage subsequently falls below 105% of VREF, the PGOOD switch is turned off and PGOOD is pulled high. PGOOD has a built-in deglitch delay of 25 µs.

Use the PGOOD signal as shown in Figure 23 for start-up sequencing of downstream converters, fault protection, and output monitoring. PGOOD is an open-drain output that requires a pull-up resistor to a DC power supply not greater than 13 V. The typical range of pull-up resistance is 10 k $\Omega$  to 100 k $\Omega$ . If necessary, use a resistor divider to decrease the voltage from a higher voltage pull-up rail.

Figure 23. Master-Slave Sequencing Power up Using PGOOD and EN

#### **Switching Frequency and Clock Synchronization**

To adjust frequency for optimizing external components for various applications, the system designer can connect a resistor from the RT pin to AGND or synchronize the SCT82A30 to an external clock signal through the SYNCIN pin.

A free-running switching frequency can be programmed from 100KHz to 1.2MHz by using a resistor from the RT pin to AGND. The frequency set resistance RRT is calculated by Equation 5. Standard-value resistors for common switching frequencies are given in Table 1.

$$R_{RT}[k\Omega] = \frac{10^4}{F_{SW}[kHz]} \tag{5}$$

| Table 1. Frequency Set Resistor R⊤ |                               |  |  |  |

|------------------------------------|-------------------------------|--|--|--|

| Switching Frequency (kHz)          | Frequency Set Resistance (kΩ) |  |  |  |

| 100                                | 100                           |  |  |  |

| 200                                | 49.9                          |  |  |  |

| 250                                | 40.2                          |  |  |  |

| 300                                | 33.2                          |  |  |  |

| 400                                | 24.9                          |  |  |  |

| 500                                | 20                            |  |  |  |

| 750                                | 13.3                          |  |  |  |

| 1000                               | 10                            |  |  |  |

| 1100                               | 9.09                          |  |  |  |

For applications with stringent frequency or interference requirements, an external clock source connected to the SYNCIN pin can be used to synchronize the high-side power device turn-on to the rising edge of the clock. The rising edge of SW voltage is phase delayed relative to SYNCIN by approximately 100ns. The SCT82A30 operates in forced continuous mode when it is synchronized to the external clock. Requirements for the external clock SYNC signal are:

Clock frequency range: 100 kHz to 1 MHz

Clock frequency: -20% to +50% of the free-running frequency set by RRT

Clock maximum voltage amplitude: 13 V

Clock minimum pulse width: 50 ns

#### **Frequency Spread Spectrum**

To reduce EMI, the SCT82A30 implements Frequency Spread Spectrum (FSS). The FSS circuitry shifts the switching frequency of the regulator periodically within a certain frequency range around the programmed switching frequency. The jittering span is ±6% of the switching frequency with 1/512 swing frequency. This frequency dithering function is effective for both frequency programmed by resistor placed at RT pin and an external clock synchronization application.

#### **Voltage Mode Control**

The SCT82A30 incorporates a voltage-mode control loop implementation. The amplitude of PWM triangle wave is larger and the pulse width has better anti-noise margin. The duty cycle adjustment is unrestricted with good response to the change of output load. Input voltage feedforward eliminates the input voltage dependence of the PWM modulator gain. This configuration allows the controller to maintain stability throughout the entire input voltage operating range and provides for optimal response to input voltage transient disturbances. The constant gain provided by the controller greatly simplifies loop compensation design because the loop characteristics remain constant as the input voltage changes, unlike a buck converter without voltage feedforward. An increase in input voltage is matched by a concomitant increase in ramp voltage amplitude to maintain constant modulator gain. The input voltage feedforward gain, KFF, is 12, equivalent to the input voltage divided by the ramp amplitude, VIN/VRAMP.

#### **Gate Drivers**

The SCT82A30 gate driver impedances are low enough to perform effectively in high output current applications where large die-size or paralleled MOSFETs with correspondingly large gate charge,  $Q_G$ , are used. Measured at  $V_{CC}$  = 7.5 V, the low-side driver has a low impedance pulldown path of 0.6 $\Omega$  to minimize the effect of dv/dt induced turn-on, particularly with low gate-threshold voltage MOSFETs. Similarly, the high-side driver has 1.3 $\Omega$  and 0.6 $\Omega$  pull-up and pulldown impedances, respectively, for faster switching transition times, lower switching loss, and greater efficiency.

The high-side gate driver works in conjunction with an integrated bootstrap diode and external bootstrap capacitor, C<sub>BST</sub>. When the low-side MOSFET conducts, the SW voltage is approximately at 0V and C<sub>BST</sub> is charged from VCC through the integrated boot diode. Connect a 0.1µF or larger ceramic capacitor close to the BST and SW pins.

Furthermore, there is a proprietary adaptive dead-time control on both switching edges to prevent shoot-through and cross-conduction, minimize body diode conduction time, and reduce body diode reverse recovery losses.

#### **Current Sensing and Overcurrent Protection**

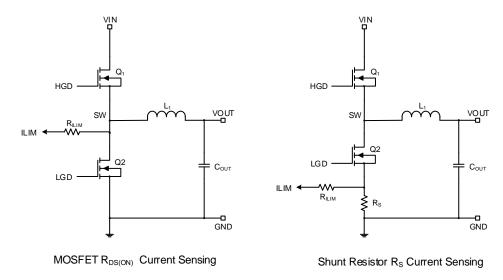

The SCT82A30 implements two lossless current sense schemes in Figure 24, using the on-state resistance of the low-side MOSFET or alternative implementation with current shunt resistor RS, limiting the inductor current during an overload or output short-circuit condition. The controller senses the inductor current during the PWM off-time when LGD is high.

The ILIM pin sources a reference current that flows in an external resistor, designated RILIM, to program of the current limit threshold. A current limit comparator on the ILIM pin prevents further SW pulses if the ILIM pin voltage goes below GND.

For more information www.silicontent.com © 2022 Silicon Content Technology Co., Ltd. All Rights Reserved 17

Figure 24. Current Sensing Schemes

Two optional connections sensing inductor current:

- R<sub>DS(on)</sub> sensing mode: R<sub>ILIM</sub> is tied to SW to use the RDS(on) of the low-side MOSFET as a sensing element.

- R<sub>SENSE</sub> shut mode: R<sub>ILIM</sub> is tied to a shunt resistor connected at the source of the low-side MOSFET.

The SCT82A30 detects the appropriate mode at start-up and sets the source current amplitude and temperature coefficient (TC) accordingly. The ILIM current with RDS-ON sensing is 200 µA at 27°C junction temperature and incorporates a TC of +4500 ppm/°C to generally track the RDS(on) temperature variation of the low-side MOSFET. Conversely, the ILIM current is a constant 100µA in RSENSE mode. This controls the valley of the inductor current during a steady state.

Depending on the chosen mode, select the resistance of RILIM using Equation 6 or Equation 7.

$$R_{ILIM} = \frac{I_{OUT} - \Delta I_L/2}{I_{RDSON}} \cdot R_{DS(ON)Q2} \quad R_{DS(ON)} \text{ sensing mode}$$

(6)

$$R_{ILIM} = \frac{I_{OUT} - \Delta I_L/2}{I_{RS}} \cdot R_S \quad R_S \text{ shut sensing mode}$$

(7)

where

- ∆I<sub>L</sub> is the peak-to-peak inductor ripple current

- R<sub>DS(on)Q2</sub> is the on-state resistance of the low-side MOSFET

- IRDSON is the ILIM pin current in RDS-ON mode

- Rs is the resistance of the current-sensing shunt element, and

- I<sub>RS</sub> is the ILIM pin current in R<sub>SENSE</sub> mode.

Given the large voltage swings of ILIM in RDS(on) sensing mode, a capacitor designated CILIM connected from ILIM to PGND is essential to the operation of the valley current limit circuit. Choose this capacitance such that the time constant RILIM-CILIM is approximately 6 ns.

Note that current sensing with a shunt component is typically implemented at lower output current levels to provide accurate overcurrent protection. Burdened by the unavoidable efficiency penalty, PCB layout, and additional cost implications, this configuration is not usually implemented in high-current applications except where OCP set point accuracy and stability over the operating temperature range are critical specifications.

SCT

#### **Device Functional Modes**

#### **Shutdown Mode**

The EN pin provides ON / OFF control for the SCT82A30. When the EN voltage is below 0.37V typical, the device is in shutdown mode. Both the internal bias supply LDO and the switching regulator are off. The quiescent current in shutdown mode drops to  $7.2 \,\mu\text{A}$  typical at VIN = 48 V. The SCT82A30 also includes under voltage protection of the internal bias LDO. If the internal bias supply voltage is below its UVLO threshold level, the switching regulator remains off.

#### Standby Mode

The internal bias supply LDO has a lower enable threshold than the switching regulator. When the EN voltage exceeds 0.41 V typical and is below the precision enable threshold 1.2 V typically, the internal LDO is on and regulating. Switching action and output voltage regulation are disabled in standby mode.

#### **Active Mode**

The SCT82A30 is in active mode when the VCC voltage is above its rising UVLO threshold of 5 V and the EN voltage is above the precision EN threshold of 1.2 V. The simplest way to enable the SCT82A30 is to tie EN to VIN. This allows self-start-up of the SCT82A30 when the input voltage exceeds the VCC threshold plus the LDO dropout voltage from VIN to VCC.

#### **Diode Emulation Mode**

The SCT82A30 provides a diode emulation feature that can be enabled to prevent reverse (drain-to-source) current flow in the low-side MOSFET. When configured for diode emulation, the low-side MOSFET is switched off when reverse current flow is detected by sensing of the SW voltage using a zero-cross comparator. The benefit of this configuration is lower power loss at no-load and light-load conditions, the disadvantage being slower light-load transient response. The diode emulation feature is configured with the SYNCIN pin. To enable diode emulation and thus achieve discontinuous conduction mode (DCM) operation at light loads, connect the SYNCIN pin to AGND or leave SYNCIN floating. If forced PWM (FPWM) continuous conduction mode (CCM) operation is desired, tie SYNCIN to VCC either directly or using a pullup resistor. Note that diode emulation mode is automatically engaged to prevent reverse current flow during a pre-bias start-up. A gradual change from DCM to CCM operation provides monotonic start-up performance.

#### **Thermal Shutdown**

The SCT82A30 includes an internal junction temperature monitor. If the temperature exceeds 175°C (typical), thermal shutdown occurs. When entering thermal shutdown, the device:

- Turns off the high-side and low-side MOSFETs.

- Pulls SS/TRK and PGOOD low.

- Turns off the VCC regulator.

- Initiates a soft-start sequence when the die temperature decreases by the thermal shutdown hysteresis of 20°C (typical).

This is a non-latching protection, and the device will cycle into and out of thermal shutdown if the fault persists.

For more information <a href="www.silicontent.com">www.silicontent.com</a> © 2022 Silicon Content Technology Co., Ltd. All Rights Reserved

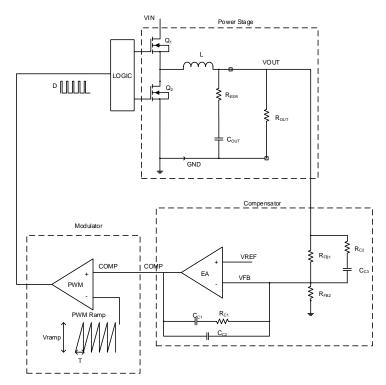

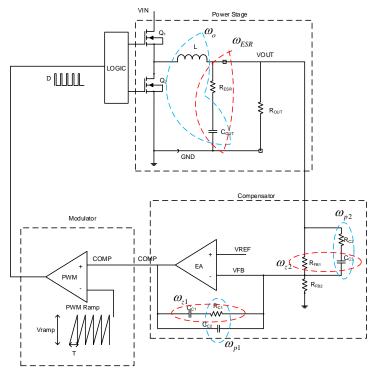

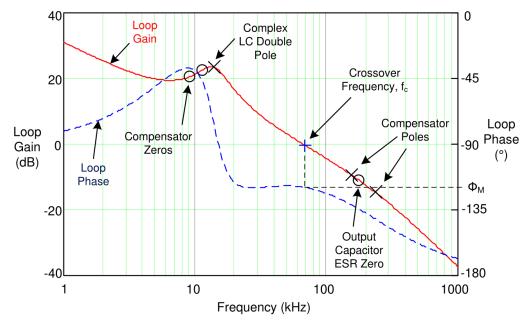

#### **Control loop compensation**

The SCT82A30 integrates the voltage mode control loop implementation and feeds the input voltage forward to eliminate the input voltage dependence of the PWM modulator gain. The voltage mode buck control loop is show as below:

Figure 25. Buck circuit voltage loop control diagram

The compensation network typically employed with voltage-mode control is a Type-III circuit with three poles and two zeros. One compensator pole is located at the origin to realize high DC gain. The normal compensation strategy uses two compensator zeros to counteract the LC double pole, one compensator pole located to nullify the output capacitor ESR zero, with the remaining compensator pole located at one-half switching frequency to attenuate high frequency noise. The resistor divider network to FB determines the desired output voltage. Note that the lower feedback resistor, RFB2, has no impact on the control loop from an AC standpoint because the FB node is the input to an error amplifier and is effectively at AC ground. Hence, the control loop is designed irrespective of output voltage level. The proviso here is the necessary output capacitance derating with bias voltage and temperature.

The small-signal open-loop response of a buck regulator is the product of modulator, power train and compensator transfer functions. The power stage transfer function can be represented as a complex pole pair associated with the output LC filter and a zero related to the ESR of the output capacitor. The DC (and low frequency) gain of the modulator and power stage is V<sub>IN</sub> /V<sub>RAMP</sub>. The gain from COMP to the average voltage at the input of the LC filter is held essentially constant by the PWM line feedforward feature of the SCT82A30 (KFF=V<sub>IN</sub> /V<sub>RAMP</sub> =12 V/V).

Complete expressions for small-signal frequency analysis are presented in Table 2. The transfer functions are denoted in normalized form. While the loop gain is of primary importance, a regulator is not specified directly by its loop gain but by its performance related characteristics, namely closed-loop output impedance and audio susceptibility.

Table 2. Buck Regulator Small-Signal Analysis

| TRANSFER FUNCTION           | EXPRESSION                                                                                                                                  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Open-loop transfer function | $T_{V}(s) = \frac{V_{comp}(s)}{V_{o}(s)} \cdot \frac{V_{o}(s)}{d(s)} \cdot \frac{d(s)}{V_{comp}(s)} = G_{C}(s) \cdot G_{vd}(s) \cdot F_{m}$ |

© 2022 Silicon Content Technology Co., Ltd. All Rights Reserved Product Folder Links: SCT82A30

| Duty-cycle-to-output transfer function | $G_{vd}(s) = \frac{V_o(s)}{d(s)} = V_{IN} \frac{1 + \frac{s}{\omega_{ESR}}}{1 + \frac{s}{Q_o \omega_o} + \frac{s^2}{\omega_o^2}}$                                                                                                      |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compensator transfer function          | $G_{C}(s) = \frac{V_{comp}(s)}{V_{o}(s)} = \frac{1}{R_{FB1}C_{C1}s} \frac{\left(1 + \frac{s}{\omega_{z1}}\right)\left(1 + \frac{s}{\omega_{z2}}\right)}{\left(1 + \frac{s}{\omega_{p1}}\right)\left(1 + \frac{s}{\omega_{p2}}\right)}$ |

| Modulator transfer function            | $F_m = \frac{d(s)}{V_{comp}(s)} = \frac{1}{V_{ramp}}$                                                                                                                                                                                  |

The compensation network typically employed with voltage-mode control is a Type-III circuit with three poles and two zeros. One compensator pole is located at the origin to realize high DC gain. The normal compensation strategy uses two compensator zeros to counteract the LC double pole, one compensator pole located to nullify the output capacitor ESR zero, with the remaining compensator pole located at one-half switching frequency to attenuate high frequency noise. The resistor divider network to FB determines the desired output voltage. Note that the lower feedback resistor, R<sub>FB2</sub>, has no impact on the control loop from an AC standpoint because the FB node is the input to an error amplifier and is effectively at AC ground. Hence, the control loop is designed irrespective of output voltage level. The proviso here is the necessary output capacitance derating with bias voltage and temperature. The poles and zeros(no include original pole) inherent to the power stage and compensator are respectively illustrated by red and blue dashed rings in the schematic embedded in Table 3.

Figure 26. Control loop with poles and zeros

| Table 5. Buok Regulator Foles and Zeros       |                                                                                                            |                                               |                                                           |  |  |  |  |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------|--|--|--|--|

| POWER STAGE POLES                             | POWER STAGE ZEROS                                                                                          | COMPENSATOR POLES                             | COMPENSATOR ZEROS                                         |  |  |  |  |

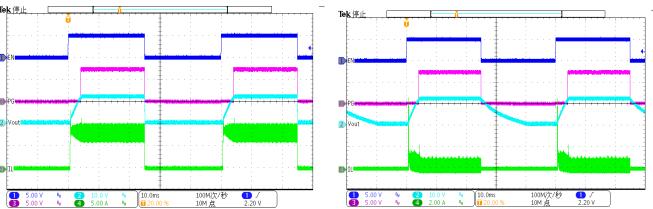

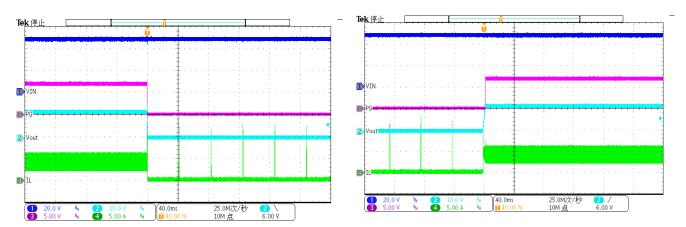

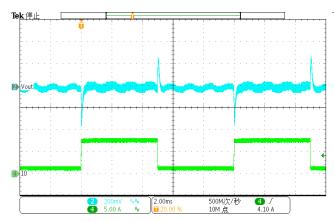

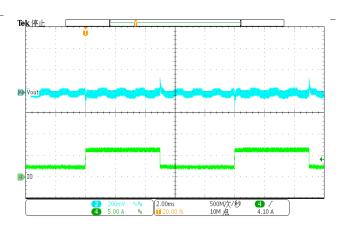

| 1 1                                           |                                                                                                            | $\omega_{p1} = \frac{1}{R_{C1} \cdot C_{C2}}$ | $\omega_{z1} = \frac{1}{R_{C1} \cdot C_{C1}}$             |  |  |  |  |